# Design and Benchmarking of Real-Time Multiprocessor Operating System Kernels

Mikael Åkerholm and Tobias Samuelsson, Masters' thesis

The Department of Computer Science and Engineering, Mälardalen University, June 2002.

# Foreword

We are cheerful to present our work to candidate for the degree of Master of Science in Computer Engineering. The work has been divided into two parts of equal weight and therefore this examination paper contains two papers that can be studied independently. The first paper is a survey and evaluation of existing real-time multiprocessor kernels. In the opening sections of the second paper we introduce an own implementation of such a kernel. The main part of the second paper presents a benchmark series, wich purpose is to compare our implementation with an existing hardware implementation.

# **Table of Contents**

A Survey and Evaluation of Real-Time Multiprocessor Operating System Kernels5Introduction and Benchmarking of Competitive Real-Time Multiprocessor Kernels87Appendix 1112

Design and Benchmarking of Real-Time Multiprocessor Operating System Kernels

# A Survey and Evaluation of Real-Time Multiprocessor Operating System Kernels

Mikael Åkerholm and Tobias Samuelsson Preparatory study for masters' thesis.

## ABSTRACT

Multiprocessor architectures, operating systems and real-time technologies are all interesting and highly advanced topics. Real-time demands inject an additional correctness criterion into computer systems. It is not just the result that is important, timing issues also have to be considered. A multiprocessor system is able to provide more performance than today's fastest single processor solution, and it is often in multiprocessor systems the latest technology is introduced. The operating system is without hesitation the most important software of all system programs in a real-time multiprocessor system.

The main limitations and concerns reported so far from the rather young research area of real-time issues in multiprocessor systems, mainly consists of schedulability problems and anomalies with old single processor scheduling algorithms. The possibilities with moving real-time applications onto multiprocessor platforms on the other hand weight more; scalability, robustness, more and cheaper computing power are the general advantages. That real-time operating systems with multiprocessor support will become a desired product in the near future is a highly realistic prediction, since the requirements and complexity of real-time applications increases rapidly.

In this survey we review and evaluate both commercial and research solutions that addresses all three attention-grabbing areas in a homogeneous manner. The paper first identifies the major design goals and key issues in multiprocessor realtime operating systems, to follow up with a set of case studies where the identified issues are unveiled.

> The Department of Computer Science and Engineering, Mälardalen University, March 2002.

| Introduction                             |     |

|------------------------------------------|-----|

| Design issues                            | 10  |

| Scheduling                               | 10  |

| Task management                          | 10  |

| Scheduling algorithms                    | 11  |

| Multiprocessor scheduling                | 12  |

| Memory management                        | 15  |

| The software layer                       | 16  |

| Real-time kernels                        | 16  |

| Interprocess Communication               | 17  |

| Resource reclaiming                      |     |

| Interrupts                               | 21  |

| Benchmarking real-time operating systems | 22  |

| Monitoring                               | 22  |

| Testing vs. benchmarking                 | 25  |

| Benchmark examples                       | 25  |

| Case Studies                             | 30  |

| Selection criteria                       | 30  |

| Evaluation model                         | 31  |

| CHAOS <sup>arc</sup>                     | 33  |

| Scheduling                               | 34  |

| Memory management                        | 35  |

| Interprocess communication               | 36  |

| Conclusions                              | 37  |

| Evaluation                               | 38  |

| Chimera                                  | 40  |

| Scheduling                               | /11 |

| Memory management                        | 41  |

| Interprocess communication               | 41  |

| Conclusions                              | 43  |

| Evaluation                               | 43  |

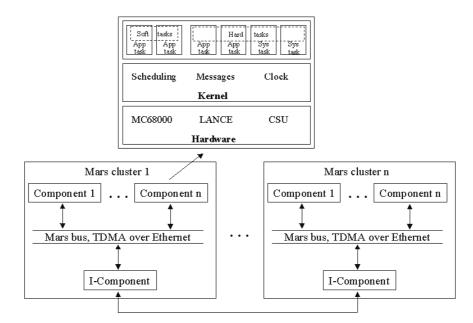

| MARS                                     | 45  |

| Scheduling                               | 46  |

| Memory management                        | 47  |

| Interprocess communication               | 47  |

| Conclusions                              | 48  |

| Evaluation                               | 48  |

| MontaVista Linux                         | 50  |

| Scheduling                               | 50  |

| Memory management                        | 51  |

| Interprocess communication               | 51  |

| Conclusions                              | 51  |

# Table of contents

| Evaluation                  | 52 |

|-----------------------------|----|

| OSE                         | 5. |

| Scheduling                  |    |

| Memory management           | 54 |

| Interprocess communication  | 5: |

| Conclusions                 | 50 |

| Evaluation                  | 5′ |

| RT-Mach                     |    |

| Scheduling                  | 5  |

| Memory management           | 6  |

| Interprocess communication  | 6  |

| Conclusions                 | 6  |

| Evaluation                  | 6  |

| RTEMS                       | (  |

| Scheduling                  | 6  |

| Memory management           | 6  |

| Interprocess communication  | 6  |

| Conclusions                 | 6  |

| Evaluation                  | 6  |

| SARA                        |    |

| Scheduling                  |    |

| Memory management           |    |

| Interprocess communication  |    |

| Conclusions                 |    |

| Evaluation                  |    |

| Spring                      | 7  |

| Scheduling                  | 7  |

| Memory management           |    |

| Interprocess communication  | 7  |

| Conclusions                 | 7  |

| Evaluation                  | 7  |

| Summary of evaluations      |    |

| Conclusions and Future Work |    |

| lcknowledgements            |    |

| References                  | 8. |

Mikael Åkerholm and Tobias Samuelsson, Mälardalen University, June 2002

# Introduction

The purpose of this survey is to review some of the major concepts concerning Real-Time Operating Systems (RTOS) aimed for parallel or distributed hardware platforms, roughly reflecting the state of the art in the early beginning of the 21<sup>st</sup> century. The work was carried out as a preparatory study to a masters' thesis project at the department of computer science and engineering at Mälardalen University.

Real-time systems are computing systems that have a time critical nature. When a certain event occurs in the environment, the real-time system must react with the correct response within a certain time interval. In ordinary systems it is typically the value of the output that determines the correctness, in real-time systems we also have the timing issues to consider. A correct output produced to late or to early could often be useless, or even dangerous. In [STA00], it is concluded that 98% of the microprocessors produced in 1998 where for real-time or embedded systems use, and towards the end of 2000 it is predicted to be up against 100%. Examples of applications that require real-time computing include:

- Vehicle control systems

- Industrial automation systems

- Telecommunication systems

- Military systems

- Railway switching systems

- Forestry automation systems

The purpose with an RTOS is to simplify the development process of real-time systems, by providing an interface with a higher abstraction level than the bare hardware architecture offers. The most distinguishing features with a RTOS compared to an ordinary Operating System (OS) are the deterministic and predictive time management. An ordinary OS often tries to perform all actions with average throughput in mind, this methods minimizes the average case at the cost of the worst-case. An RTOS must try to handle all system calls and task switches in a predictive and analysable manner, i.e. often by providing a known worst-case behaviour.

The demand for distributed or parallel hardware architectures in real-time systems as other systems is mainly due to the fact that the applications requires more than a single processor can offer. Complexity in real-time systems increases more rapidly than the performance of the microprocessors increases. A special demand exists in some real-time systems; since many real-time applications are distributed by its nature it is motivated to use a distributed control system. Consider industrial manufacturing pipelines with several robots, the robots is performing independent work but it is easy to understand that the robotics must be synchronized in some way. Many slightly different interpretations of the difference between a parallel and a distributed hardware platform exist. In this survey the difference is defined by the tightness of the connections in the machine, if a processor in the machine requires at least one common and shared resource or device to be working properly it is a parallel machine. In a distributed architecture it is assumed that a processor can be taken out together with its own private devices and resources, without ruin the possibility to use the rest of the system and the detached processor as two independent computers. The term multiprocessor is sometimes used to address only parallel computers, but in some cases both distributed and parallel architectures, it should be no problem to distinguish between the cases when that is necessary. Finally the term multi computer is a true distributed architecture.

The authors are not aware of any surveys with the same objectives as this, but it exists many papers and articles specialized towards a narrower subject covered by this survey and surveys with slightly different objectives. In [YAN97], the authors presents a survey directed towards RTOS, but no RTOS is described in detail it is rather a design issue survey. A chapter in [BUT97] presents some RTOS, described as a survey, but the selection criteria differs from ours. The survey is not directed through multiprocessor or distributed hardware platforms, although some RTOS with support for such target platforms are mentioned. A operating system survey that is directed towards multiprocessor platforms but not real-time kernels is [GOP93].

The outline of the survey is as follows. In the design issues section we will try to discover and explain the most important issues in multiprocessor RTOS and how they can be compared to each other. The next section is a case study of a set of selected RTOS with multiprocessor support, each RTOS central concepts will be presented and an evaluation will follow every RTOS description. The final section concludes the survey and discusses future work.

# **Design issues**

In this section a framework for description and evaluation of real-time multiprocessor operating systems are presented. We are aware of that many important aspects of an operating system have been left out, mainly due to the need of limit the survey. The issues we have left out include areas such as structure and I/O. The structure of operating systems is typically referred to as monolithic, layered or client-server based. Areas sorting under I/O are disks, user interactions and environment sampling. I/O, structure and most of the other issues we are not addressing are described in [TAN92]. The three central issues, which describe almost all essential constructs in a real-time operating system, are:

- Scheduling

- Memory management

- Interprocess communication

In the first part of this section an explanatory presentation of the three mentioned issues is given, together with an introduction to some of the presented algorithms and ideas designed for usage within the three specific areas. In the end of the section benchmarks as method for practical comparison of RTOS:es are reviewed. Although this survey only evaluates different RTOS:es theoretically, a well and fair performed benchmark is often the most reliable basis for a comparison.

### Scheduling

The first issue to address when talking about scheduling algorithms for real-time systems is the task management. With task management, we basically mean attributes associated to tasks. This is an important issue since different scheduling algorithms require different task attributes, and different real-world problems are often easiest to express with different task attributes.

#### Task management

The basic terms concerning tasks and their attributes are easiest explained by an example. A real-time system is a system that interacts with the environment by performing pre-defined actions on events within a certain time. The action of a special event is typically defined in a *task* and within a certain time forms the *deadline* for a task. A real-time task can be classified as *periodic* or *aperiodic* depending on its arrival pattern and as *soft* or *hard* based on its deadline. Tasks with regular arrival times are called periodic and tasks with irregular arrival times are aperiodic tasks. Each of the hard tasks must complete execution before some fixed time has elapsed since its request, i.e. finish before its deadline. Soft tasks do not have any demands in time, which means that soft tasks do not have any deadlines. Other attributes associated with a real-time task that usually are mentioned in scheduling and task management contexts are for instance:

- *Worst Case Execution Time* (WCET) is the maximum time necessary for the processor to execute the task without interruption.

- *Release time* is the time at which a task becomes ready for execution.

- *Sporadic task* is an aperiodic task with a known *minimum interarrival time* (MINT), that is the minimum time between two activations.

- *Precedence constraints* are constraints about the order of task execution, some tasks must execute in a defined order.

In almost all real-time operating systems, the information about a task is stored in a data structure, called the *task control block* (TCB). The TCB typically contains the task state, the desired or required set of attributes from those defined above, a pointer to the procedure that represents the task and a stack pointer. If the scheduling algorithm is preemptive the TCB must contain everything that is needed to store and reload the state for the task (registers etc). The rest of the content in the TCB varies from one RTOS to another; many of the special features of an RTOS will affect the TCB.

In almost all operating systems, a task can at any point in time be in one of the following *states: Running, Ready* or *Waiting.* The states may have different names in different operating systems, but the semantic meaning is always the same. Additional states exist in most operating systems, but these three states are the most important and basic states. Only one task per processor can be in the Running state at any instance in time, it is this task that currently uses the processor. A task that has all that is needed to execute, but for any reason waits for another task is said to be in the Ready state. Finally a task that misses something, a shared resource, waiting for an external event or waiting for its release time etc is said to be in the Waiting state.

#### Scheduling algorithms

Scheduling real-time systems are all about guaranteeing the temporal constraints (deadlines, release times and so on). Two main approaches for real-time scheduling exist. On one side we have off-line scheduling, where all scheduling decisions is calculated by the system designer before runtime and stored in a runtime dispatch table. The other approach is on-line scheduling, where all scheduling decisions is calculated by the scheduling algorithm at run-time. Throughout this text both the terms on-line and off-line scheduling as well as runtime and pre-runtime scheduling are used.

Which algorithm that is best suited depends on the scheduling problem to solve. For instance algorithms based on the off-line scheduling approach are more deterministic, and it is easy to prove and show that a task will meet its deadline since the methods in some sense applies the "proof-by-construction" approach. Off-line scheduling methods can also solve tough scheduling problems with high CPU utilisation and complicated precedence constraints. An off-line scheduler can spend long time in finding a suitable schedule, since the system is not up and running and no deadlines will be missed during the search, but at run-time the only scheduling mechanism we need is a simple dispatcher that performs a table lookup. On the other hand, we need to know almost everything about the systems

timing constraints to be able to create a suitable schedule before run-time. Algorithms based on the on-line scheduling approach in general offer higher flexibility and are better to adopt changes in the environment, at a higher cost for calculating on-line scheduling decisions and they cannot offer the same degree of provable determinism. The higher flexibility offered by on-line scheduling approaches cause that most existing algorithms that schedule aperiodic tasks use the on-line scheduling approach.

Most off-line scheduling algorithms that have been implemented are based on some kind of search technique with applied heuristics. Examples of such scheduling algorithms are *A*\* and *IDA*\*, they are analysed and described in [FOH94] (chapter 3). Other examples are *branch-and-bound* [RAM90] and *meta* [FOH97]. According to [JXU93] most practitioners working on safety-critical hard real-time systems, that uses the off-line scheduling approach have been observed doing the schedules by hand instead of letting a computer search for a schedule, the result (the by hand created schedule) is often hard to verify and maintain. Examples of on-line scheduling algorithms that handle periodic tasks are *Earliest Deadline First* (EDF) [LAY73], and *Rate Monotonic* (RM) [LAY73], both introduced in the early seventies. Most on-line scheduling algorithms use one of these two algorithms as base algorithm. A sample of on-line algorithms that handles both periodic and aperiodic tasks is *Sporadic Server* (SS) [LEH93], *Robust Earliest Deadline (RED)* [BUT93] and the *Total Bandwidth Server* (TBS) [BUT94].

#### Multiprocessor scheduling

The multiprocessor scheduling anomalies that do not exist in the single processor case and must be considered when constructing a multiprocessor scheduling algorithm are in brief that; the schedule length can be increased by:

- Increased number of processors

- Reduced task execution times

- Weaker precedence constraints

As a consequence when using multiprocessor platforms, algorithms that have been showed to be optimal in any sense on a uniprocessor system are often not optimal in a multiprocessor system. For instance EDF has been showed to be an optimal algorithm, under certain conditions in [DEZ74] for a uniprocessor system. In the multiprocessor environment, EDF and other under any conditions optimal on-line algorithms fails to be optimal, in [MOK83] it is showed that no algorithm can be optimal in an on-line scheduled multiprocessor system, with or without precedence and mutual exclusion constraints. Multiprocessor architectures combined with real-time scheduling are therefore a delicate problem and an ongoing research area. It is clearly easier for an off-line scheduler to be optimal, since the time that such a scheduler may consume is potentially unlimited. For instance consider an off-line scheduler that tries all possible combinations on all processors, if a schedule that solves the problem exists this scheduler will find it. Hence we can say that such a scheduler would be optimal, but it will not be practically useable since the time required finding the schedule also are not unlimited. When implementing an off-line algorithm for finding a schedule that solves a specific scheduling problem, it is easy to understand that the total time spent finding a schedule simplified is a formula as below.

(*Time not finding a schedule \* Number of failures*) + (*Time for finding \* 1*)

Through a quick look at the formula we can see that the biggest time is spent in (not finding any schedule), hence it is at least as important for an off-line scheduling algorithm to fast detect that there is no solution as actually finding a schedule. This is the main reason why no one uses our intuitive, although clearly optimal suggestion of pre-runtime scheduling algorithm.

In [STA98] the authors identifies three phases in the scheduling procedure of a multiprocessor system, and the text is directed towards on-line scheduling. The phases also seem to be suitable for an off-line scheduler. In the off-line scheduler case phases 1 and 2 would be executed off-line, and only phase 3 would be executed on-line.

- 1. Allocation the assignment of tasks and resources to the appropriate nodes or processors in the system.

- 2. Scheduling ordering the execution of tasks and network communication such that timing constraints are met and the consistency of recourses is maintained.

- 3. Dispatching executing the tasks in conformance with the scheduler's decisions.

To continue the opened discussion and get a little bit more concrete examples on a run-time, a pre-run-time and a combined approach will be given. However these algorithms assumes a lot of parameters and may be targets for some modifications and simplifications before they are applicable in the real world.

#### An on-line method

A holistic approach based on EDF is presented in [STA98]; the method is focused on how to perform the analyses so that we can guarantee deadlines on events. In the end, real-time scheduling is about being able to guarantee the temporal behaviour of a system. The method is an adoption of the holistic approach based on static rate monotonic priorities developed in [TIN94]. The assumptions limits the algorithm to be used anywhere without modifications, for instance tasks are statically allocated to a node, and a token-ring based communication medium is assumed. The original method, from [TIN94] has been adopted for use on other communication networks as well. For instance in [NOR00] examples on how to use the method with rate monotonic priorities and a CAN bus is showed. Each node has a ready queue that is scheduled by EDF and the key to overcome the otherwise hard global analysis is *attribute inheritance*. Every message inherits two of the sending tasks temporal attributes, the period and the *release jitter*. The release jitter is simply defined to be the difference between the sender tasks earliest start-time and worst-case response-time. The period that is inherited is simply the period of the task. Based on that simple notation it is possible to perform *end-to-end* response time analysis of a transaction. The iterative analysis formula can be expressed as following:

- 1. Set all initial release jitter to zero.

- 2. Compute the worst-case response-time for tasks and messages for each host processor and network separately.

- 3. Compute the worst-case jitter that the response-times in step 2 can generate, go to step 2 if the jitter does not change, else we are done.

Each of the different computations in the steps 1, 2 and 3 are quite simple summations and can be found in [STA98], however they are iterative and with many tasks it may take a while to achieve convergence.

#### An off-line method

A heuristic method for multiprocessor systems dealing with hard periodic tasks is the *Slack method* [ALT98]. Many of the offline methods only deal with this task type. The method is divided into two sub-steps named Graph Reduction and CP-Mapping. In reality we can conclude that the division into three steps easiest describes the algorithm, since two sub steps are included in the Graph Reduction step. Here comes a brief overview of the method, for a complete and detailed description with proofs and formal mathematical definitions refer to [ALT98].

During the initial Graph Reduction step, transactions (consisting of several tasks) are treated separately. Each transaction graph is taken as input to the step.

- 1. First the Graph Reduction step tries to reduce each transaction graph to a CP graph, by a method named *critical path clustering*. Critical path clustering is about finding the *critical path* of a transaction. The critical path is in short defined as the path with the smallest slack, and the smallest slack of a path is in turn defined as the minimum slack of all vertices of a path. The slack is determined as the time between a tasks deadline and the summation of the computation time and the release time, i.e. the time a task can be delayed without missing its deadline.

- 2. Secondly the Graph Reduction step tries to fill slack intervals in the generated CP graphs, with other paths. This is an initial step to let different paths execute on the same processor.

- 3. Finally the CP-Mapping step is executed. In this step the different CPgraphs, which represents one transaction each are mapped onto a physical processor. A CP-graph is a drastically reduced form of the initial problem formulation; the two reductions executed in the Graph Reduction step are successful in most cases. Hence an optimal algorithm is used for the

mapping in this step, by optimal we mean an algorithm that finds a solution if a solution exists. It is simple to construct an optimal algorithm and here *backtracking* is the choice, i.e. if any deadlines are missed during an assignment, backtrack to the next possible assignment.

#### A hybrid method, integration of off-line and on-line

A detailed explanation and description of the *Slot Shifting* algorithm can be found in [FOH95], here comes an introductory description. The Slot Shifting algorithm is an algorithm that combines both on-line and off-line scheduling. Easily we can state that the Slot Shifting algorithm handles periodic tasks with the off-line approach and that the aperiodic tasks are on-line scheduled using the remaining capacity. The algorithm uses time slots as the basic abstraction for the system time; a slot is an interval of time with a fixed length.

The off-line preparations for slot shifting is basically about creating and ordinary off-line schedule and determining spare capacities, i.e. how many time units (slots) we can move a tasks execution without jeopardizing its deadline. The task assignment to different nodes in the system is done manually or with another algorithm, task assignment is not specified in the original algorithm. Further on the network between the different nodes are assumed to be a time slotted architecture, i.e. token-ring, TDMA etc. The messages on the network is integrated in the off-line scheduling procedure. The time model is said to be discrete, since both the communication medium and the scheduling algorithm uses the same globally synchronized time slots.

The online scheduler is invoked after each slot and checks whether we have any aperiodic tasks to schedule. If aperiodic tasks are pending, the scheduler performs an on-line guarantee test. The scheduler tries to shift the execution of the periodic tasks as much as possible without risking their deadlines, using the off-line calculated spare capacities. If we have enough spare capacity to serve the aperiodic requests, we execute them else they are rejected.

### **Memory management**

When implementing a suitable memory abstraction in the operating system, the first thing to study is what the hardware offers. Many attempts for classification of hardware memory systems exist. In this survey it is the terms *Uniform Memory Access* (UMA), *Non Uniform Memory Access* (NUMA) and *NO ReMote Access* system (NORMA) that are used.

- In UMA architectures, memory access times are equal for all processes to the whole address space. A common design technique for those systems is processors connected to a bus, and a global shared memory connected to the same bus.

- The NUMA systems also offers a single shared address space that is visible for all processors, but the access times for a processor to different

memory region differs. A common design technique is processor boards with own memory modules attached to a shared bus.

• NORMA architectures on the other hand do not offer a global shared address space. Each processor just accesses its own address space. Typically these architectures consist of loosely coupled independent computers connected through ordinary *Local Area Network* (LAN) technologies, often referred to as clusters. But bus based NORMA systems are also common.

#### The software layer

Usually the operating system implements some memory abstractions above the abstraction offered by the hardware. Typically *protection*, *virtual memory*, *allocation* and *de-allocation* primitives are implemented in the operating system. Although some parts of the protection and virtual memory support often are implemented in hardware, it is the operating system that configures the hardware and implements own abstractions. Protection is about associating attributes with memory segments like read-only access or read-write access. Virtual memory means that we use more memory than is physically available. This is accomplished by introducing another bigger but considerably slower level in the memory hierarchy, i.e. a disk device. Allocation and de-allocation is about allocation is about associating run-time. Another example of typical implementation in the software layer is another memory abstraction than the hardware offers, for instance NUMA from NORMA, an example of this is described under the interprocess communication section.

#### **Real-time kernels**

Real-time kernels memory management services are often simple and primitive, almost non-existent. Virtual memory are for instance often considered as a dangerous and unreliable feature, and therefore not implemented. This is easy to understand because of the unpredictable long access times to a memory page on a disk device. It is easy to agree with the authors of [BEN01], when they state that most of the proposed software algorithms and hardware support in commercial processors for memory management are optimized for average performance, and not for predictable worst-case behaviour. Dynamic allocation of memory is also avoided, since the behaviour is both temporal and functional unpredictable. We cannot guarantee that memory will be available, and not how long it will take for the kernel to find the necessary amount of memory. Another task may allocate memory, but some semantic fault may cause the task to never de-allocate the memory. Such tasks are said to leek memory. To be completely secure against memory leaking tasks, real-time kernels often do not implement dynamic memory handling. According to this it sounds like memory management in real-time systems is rather boring, but it is not, some more fancy techniques have been presented recently.

In [BEN01], the authors develop theories for integration of virtual memory and the other functions a modern processor offers through its Memory Management Unit (MMU). Their approach is motivated by the fact that many safety-critical real-time applications consist of both hard and soft real-time tasks, i.e. hard or soft deadlines. Suitable processors for their approach are processors, which have support for some kind of partitioning of the address space. The introduction of *real-time address spaces* is the proposed solution. Tasks with soft deadlines can utilize all fancy mechanisms offered by the processor, and resides within an ordinary address space. For instance we can have a monitor task with a soft deadline that sometimes need virtual memory. While tasks within a real-time address space does not use any virtual memory or caches. Those tasks need a predictable memory access time. The definition given in [BEN01] of a real-time address space is quoted below.

"An address space is a real-time address space if: The worst-case execution time of the virtual-to-physical translation for all pages that do not result in a page fault in the address space is known."

The principle for an implementation of real-time address spaces is described for PowerPC, MIPS and StrongArm in [BEN01].

Research efforts that pay attention to real-time systems and dynamic memory management, currently seems to be driven by the need of virtual and dynamic memory in programming languages like java and C++. It is possible to use a hardware module for memory allocation; in this way we could get predictable allocation time. The *Active Memory Module* (AAM) [SRI00] is such a device. All allocations are bounded to 14 clock cycles; a fast and constant allocation time makes this device suitable for real-time applications. The AAM module was developed for the use of Java in real-time applications. The garbage collection and dynamic memory allocations naturally existing in a Java program jeopardizes the execution times. The garbage collection and dynamic allocations in Java utilizes only heap memory, so the AAM module only administrates the heap memory. The RAM module and the AAM module is physically separated, an AAM module consists of memory modules and a controller.

### **Interprocess Communication**

Communication is a central component in any operating system; especially in multiprocessor operating systems communication has the same importance as the instruction set has in a uniprocessor system. Co-operating processes or threads often communicate and synchronize. The execution by one certain process can affect another process by communication. Generally there are two different types of interprocess communication (IPC) for multiprocessor systems: message passing and shared memory.

Each of these communication models was developed for a different class of multiprocessors, reflecting the assumptions about the underlying hardware. The shared memory model is typically associated with tightly coupled shared memory multiprocessors (UMA, NUMA), while the message passing model is typically associated with distributed memory multiprocessors or distributed multicomputers (NORMA), which is a network of workstations.

Performance comparisons between message passing and direct use of shared memory have been done in [LEB92]. The authors claim that both communication models have performance advantages and the factors that influence the choice of model may not be known at compile-time. Their conclusions were mainly that the advantage with the shared memory model is load balancing, while the main advantage with the message-passing model is locality. Today both communication models are in use on both classes of machines.

In a shared memory multiprocessor, message passing is a more abstract form of communicating than accessing shared memory locations. Message passing subsumes communication, buffering and synchronization. Multiprocessor operating systems have experimented with a large number of various communication abstractions [GOP93], including *ports*, *mailboxes*, *links* etc. In other words these abstractions are kernel-handled message buffers. The two basic message-passing primitives in such abstractions are *send* and *receive*. Sends and receives may provide synchronous and/or asynchronous communication and they may be blocking (a process does not wait for the communication to complete) or non-blocking (a process waits for the communication to complete).

Computing large or complex data structures may be inefficient or difficult using message passing in a distributed memory multiprocessor or distributed multicomputer. A solution to this problem is to use coherent distributed memories, based on a message passing mechanism. As an example of such a system we refer to *Mirage* [FLE89]. Mirage is a protocol that hides the distributed memory network boundaries for the application programmers, i.e. used when the shared memory model are desirable on a distributed memory multiprocessor.

The difference between communication in a real-time system and a conventional (not real-time) system is their different system requirements. The major desirable characteristic in a conventional system is performance, expressed in throughput, average response time or latency. Real-time tasks must not only produce the correct results, they also have to be produced *on time*. However, this cannot be achieved by just providing a fast communication media. In conventional systems, IPC can be unpredictable due to the potentially unlimited blocking time of applications synchronizing or waiting for messages. So the communication in real-time systems must not only be fast, it must also be predictable and deterministic, in order to guarantee hard tasks by using some form of analysis before the start-up of the system (pre-runtime). A method to make IPC efficient is

to implement hardware support for such functionality [FUR01]. The main drawback with IPC mechanisms implemented in special purpose hardware is the cost of extra hardware.

### **Resource reclaiming**

A shared resource is a software structure that can be used by more than one process to advance its execution. Any operating system that supports shared resources must provide any resource access protocol to ensure consistency of the data in the shared resources. In other words the operating system must guarantee mutual exclusion (for instance by providing semaphores) among competing tasks, so if two or more tasks have resource constraints, they must be synchronized. Intertask communication is a critical issue in real-time systems, since the fact that shared resources may cause priority inversion [BUT97] and unbounded blocking on processes' executions. A priority inversion occurs when a high-priority task requests a shared resource that is used by a low-priority task. This means that the high-priority task must wait for the low-priority task to finish its execution, i.e. the high-priority task executes with a lower priority than the low-priority task. Since the duration of priority inversion in general is unbounded, this jeopardizes the predictability of tasks execution. There are many different approaches to solve the priority inversion problem. The Priority Inheritance and the priority ceiling protocol are two semaphore protocols where the maximum blocking time for a task can be calculated.

#### Priority Inheritance Protocol

The priority inheritance protocol, proposed by Sha, Rajkumar and Lehoczky in [LEH90], minimizes the blocking time of a high-priority task by increasing the priority of the low-priority task when the high-priority task becomes blocked. A task can only hold semaphores during the execution, i.e. when a task has finish its execution it is not allowed to hold any semaphores.

Definition of the Priority inheritance protocol:

- 1. Task A executes and tries to obtain semaphore S. If semaphore S is locked, task A is blocked because it cannot lock the semaphore, if not task A locks semaphore S. When A unlocks S, the task with the highest priority that is blocked by A becomes ready.

- 2. Task A uses its assigned priority during execution unless it has locked semaphore S and blocks higher-priority tasks. If task A blocks higher-priority tasks, it will execute with the highest priority of the tasks that is blocked by A (A inherits the highest priority). When A unlocks semaphore S, A will return to its original priority.

- 3. Priority inheritance is transitive. Assume three tasks A, B and C in descending priority order. If task C blocks B and B blocks A, task C will receive task A's priority.

A drawback with the priority inheritance protocol is that it does not deal with blocking-chains and deadlocks.

#### Deadlock

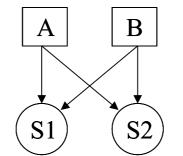

Deadlocks are best described with an example. Assume two tasks A and B that both want semaphores S1 and S2. Task A has high priority and task B has low priority. Task A attempts to lock semaphore S1 before S2, while B attempts to lock S2 before S1. We have the situation illustrated by Figure 1.

Figure 1, A and B are tasks, S1 and S2 are semaphores.

A deadlock scenario:

- 1. All semaphores are free.

- 2. Task B locks S2.

- 3. Task A preempts B and locks S1.

- 4. Task A attempts to lock S2, but S2 is locked so A is blocked.

- 5. Task B attempts to lock S1, but S1 is locked so B is blocked.

- 6. Both tasks are blocked, waiting for each other. A deadlock has arisen.

A solution to the deadlock problem is to use the Priority Ceiling Protocol, which is described in the next section.

#### Priority Ceiling Protocol

The priority ceiling protocol [LEH90] minimizes the blocking time of highpriority tasks by preventing blocking-chains. Furthermore this protocol prevents deadlocks.

Each semaphore S is assigned a priority ceiling. The value of the ceiling is equal to the priority of the task that has highest priority among those tasks that want to lock semaphore S.

Definition of the priority ceiling protocol:

1. Task A executes and attempts to lock semaphore S. Let S\* be the semaphore with highest priority ceiling among those semaphores that currently are locked. Task A cannot lock semaphore S if it is already locked, so A is blocked. If semaphore S is not locked, A locks S in case A's priority is higher than the priority ceiling for S\*. The task with

highest priority among those tasks that are blocked by A, becomes ready when A unlocks S.

2. Task A uses its assigned priority during the execution in case it has not locked a semaphore S and blocks higher-priority tasks. If task A blocks higher-priority tasks, it will execute with the highest priority of the tasks that is blocked by A (A inherits the highest priority). When A unlocks semaphore S, A will return to its original priority.

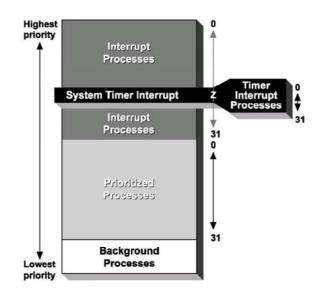

#### **Interrupts**

Interrupts generated by external I/O devices causes a big problem for the predictability of real-time systems, because if they are not properly handled they may introduce unbounded delays during process execution. In most operating systems, the arrival of an interrupt starts the execution of an interrupt service routine (driver), dedicated to the management of the certain device. With this approach, all hardware details of the device are encapsulated inside the driver. An interrupt service routine should be as small as possible, i.e. handle the device that generated the interrupt in order to minimize the blocking time of ordinary tasks. Often this means that the interrupt service routine reads or writes a value to the device and then just acknowledges the interrupt. Typically the interrupt service routine often sends the received value to a task that further serves the value.

In many operating systems, interrupts are served using fixed priority schemes, i.e. each driver is scheduled based on a static priority, which is higher than the process priorities. This is motivated by the fact that I/O devices normally deals with real-time constraints, whereas most application programs do not. An important real-time issue with interrupt handling is systems maximum interrupt latency, i.e. how long time can the system turn off all interrupts (interrupt disable).

Next a brief description three different approaches will be given.

1. This approach eliminates interrupt interference by disabling all interrupts except the timer interrupts, which are necessary for the system. Since no interrupts are allowed, application tasks handle the external devices through polling. This strategy requires that the application tasks have direct access to the I/O devices that they want to handle. All device-dependent functions can be encapsulated in a set of library functions; so different application tasks can include different libraries. An advantage with this function is that the kernel does not need to be modified when new I/O devices are added. The main drawbacks with this approach are the response times of external devices and the processor utilization on I/O operations. A system that has adopted this approach is RK, which is a hard real-time kernel for multi-sensor applications [LEE88].

- 2. The second approach resembles the previous one, because all interrupts except from the timer are disabled. Instead of using application tasks for handling devices, this method uses dedicated kernel routines to serve devices. The timer periodically activates the kernel routines. This strategy eliminates the unbounded delays due to the execution of the interrupt drivers and all device-dependent functions are encapsulated in kernel routines and do not need to be known to the application tasks. In comparison with the previous approach this strategy has a little higher system overhead, because of the required communication between the kernel routines and the application tasks for exchanging I/O data. This approach has for instance been adopted in the MARS system [KOP89].

- 3. The third approach enables all interrupts, but the drivers must be reduced to the least as possible. The only purpose of the drivers is to activate a certain task that will handle the management of the device, i.e. the driver do not handle the device directly but only activates a dedicated task. The device management tasks are scheduled and guaranteed as all ordinary tasks. The major advantages with this method in comparison with the previous described approaches are the elimination of the busy wait I/O operations, that a control task can have a higher priority than a device-handling task. A system that has been adopted this approach is the SPRING system [MOL90], which is a distributed real-time operating system for large complex applications with hard timing constraints.

### **Benchmarking real-time operating systems**

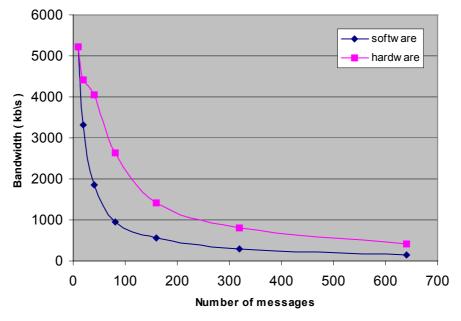

Benchmark programs measure the relative speed of computers, algorithms or different language implementations. Usually they are used when performance comparisons are to be carried out. For instance, benchmarking can be used to compare a software implementation with a hardware implementation, since the approach: using special-purpose hardware for increasing the performance and predictability of a system is widely used today. Another way of using benchmarks is when a novel system with performance requirements has been developed. In such case, the benchmark program works as a software verification tool. A problem with benchmarking of real-time operating systems is the lack of standards for measuring performance [ACH91, WEI99]. Especially when evaluating real-time kernels from different vendors, the tests often have to be rewritten, because the kernels have interface differences.

#### Monitoring

In order to benchmark a system, the system has to be monitored, i.e. gathering run-time information for performance measurements. Any attempt to gain more information about a system may intrusive the system temporal and/or functional. This problem has been referred to as the *probe-effect*. Probes are necessary for monitoring; without probes it is impossible to measure a systems performance. When the programmer has monitored a system by using probes, the probes cannot

be removed in all cases. Because, an elimination of the probes may also introduce the probe-effect. That means that the probe-effect may occur either when probes are inserted into the system or when probes are removed from the system.

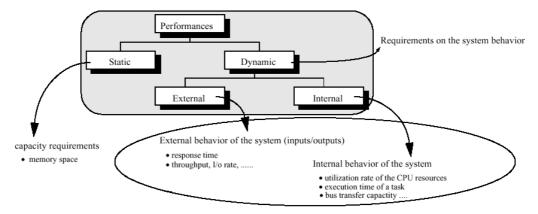

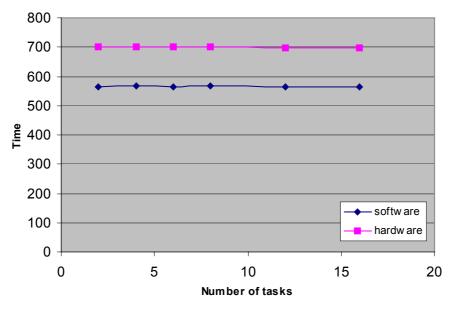

A system may have performance requirements. In such case, the designers must first estimate the performance of the architecture during the design phase, and when the system has been tested, measure and evaluate the real performances and compare them to the performance requirements. In [CAL98], the authors have classified different kind of performances into different categories, see figure 2. Dynamic performances are classified into external performances that concern the behaviour of the system observed from its interface (response time, throughput etc.) and internal performances (process execution time, bus utilization, etc.). The dynamic performances are the most difficult to deal with.

Figure 2, Different categories of performances.

The problem of collecting relevant information from distributed real-time systems can be classified in three categories: hardware monitoring, software monitoring and hybrid monitoring.

The hardware monitoring is based on connecting probes to the hardware system in order to observe its behaviour without disturbing it. The probes can for instance be logic analyzers or emulators. The main drawbacks according to [CAL98] are:

- Often the development of a specific hardware and software to monitor it are required.

- The abstraction-level of the collected information is very low, which makes it difficult to interpret.

- With future VLSI components including all the parts (CPU, memory, FPGA) in the same chip (system-on-chip), this technique does not work.

The software approach consists of adding a set of extra instructions to the software, in order to collect all useful information during runtime. This technique

can be fairly target independent, with focus on the hardware architecture. It also provides a high level of abstraction of the collected information. The major drawback with this approach is the disturbance on the system, affected by the information gathering. Both the temporal and system behaviour may be disturbed. For real-time applications, the disturbance may end in both wrong results and not fulfilled timing constraints.

The hybrid approach is a combination of software monitoring and hardware monitoring. It is based on a few instructions in the software code that selects adequate information. The information is collected with a specific hardware, and then transmitted to a host system [CAL98].

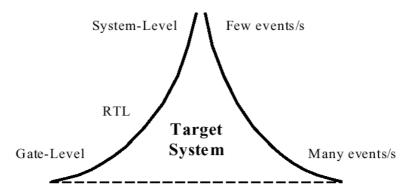

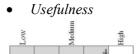

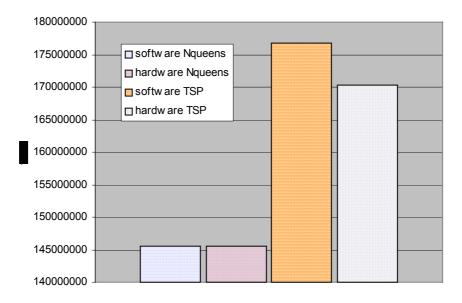

A hardware approach that overcomes the main drawbacks with hardware monitoring listed in [CAL98], is MAMon (Multipurpose/Multiprocessor Application Monitor) [SHO01], which is an ongoing research project at Mälardalen University. MAMon can be integrated in a System-on-Chip (SoC) design and it increases the level of abstraction. The current version of the monitoring system can both monitor the logic-level and the system-level in both single and multiprocessor systems. The monitoring system is able to monitor in a completely passive manner without probe effect, assuming an ideal target system. Ideal target systems are systems were a small hardware component could be integrated in the hardware as a SoC or a hardware kernel as the RTU [ADO96]. Today many SoC applications are hard to verify and optimize, they are often monitored from the register transfer level (RTL) or even the gate-level. Bugs are however easier to find in the system-level since fewer events/s occurs on that level [SHO01] as illustrated in figure 3, this motivates a top-down debugging strategy. MAMon allows us monitoring the system-level, this might be important in future SoC applications since complexity is increasing with a tremendous speed.

Figure 3, Events/s in different abstraction levels.

#### Testing vs. benchmarking

Software testing is often associated with the terms *validation* and *verification*. Validation is the process of checking that a programs specification fulfils the customers' requirements. Software testing is a kind of verification of a program or system, with consideration to the specification. In general, two methods can be applied in the verification process, namely testing and formal methods. Today, testing is the state-of-practice, although formal methods seem to be a powerful tool, many problems must be solved before formal methods can replace testing in complex real-time systems. In [THA00], the author explains the main limitations with today's formal methods. For instance it is at least as error-prone to express systems functionality in a formal mathematical language as writing the code, and it is also hard to verify that it is the "real system" that is modeled. The interested reader can consult [BAR92], for more information on how to use formal methods in the software verification process.

Software testing is used in the verification-process of a program or system, with consideration to the specification. Testing may be divided into two stages. First, a kind of testing strategy is developed. The testing strategy describes how testing is to be performed, i.e. how to select input data, what information have to be collected and how to collect and analyze this information. Second, the testing strategy is applied to a program, which results in a test of that program.

Benchmarking is used with completely different goals in mind, than verification. The purpose with a benchmark is to create basis for comparisons of systems, or products with similar properties [KAM96]. In other words a suitable benchmark must include and cover the most typical properties of the target applications.

#### **Benchmark** examples

In this section some suitable *benchmarks for real-time operating systems* are presented and described. Classes of benchmark techniques that are skipped in our selection include *microprocessor-oriented benchmarks*. When designing a real-time or embedded system, microprocessor-oriented benchmarks are used to assist the designer in the comparison between different hardware platforms. Some examples of microprocessor-oriented benchmarks can be found in the Whetstone [CUR76] and the Dhrystone [WEI84] benchmarks. These benchmarks are widely used and have own metrics associated with them, whetstones and dhrystones. Both benchmarks are based on synthetic workloads, the Whetstone benchmarks represents a typical scientific workload while the Dhrystone benchmarks represents a typical system program instruction stream. Instead of assisting the designer to choose the most suitable hardware platform, the following methods are used for performance measurements.

#### Rhealstone

The Rhealstone benchmark [KAR89] is a real-time microbenchmark, based on the idea that each real-time application is unique, in contrast to Dhrystone and Whetstone. First of all, six categories of components that are crucial to the performance of real-time systems are measured and summarized:

- 1. *Task switching time* The average time the system takes to switch between two independent and active tasks of equal priority

- 2. *Preemption time* The average time it takes a higher priority task to take the control of the system from a low priority task. In general this event occur when a high priority task becomes ready.

- 3. *Interrupt latency time* The time between the CPU's receipt of an interrupt request and the execution of the first instruction in the interrupt service routine (ISR).

- 4. *Semaphore shuffling time* The delay of a task releasing a semaphore, and the activation of another task waiting for that semaphore. No other tasks are scheduled in between.

- 5. *Deadlock breaking time* The average time it takes to resolve a deadlock, which occurs when a high priority task preempts a low priority task that hold a resource needed by the high priority task.

- 6. *Datagram throughput time* The number of kilobytes per second one task can send to another, by using kernel primitives, i.e. the average interprocess communication speed.

Measurement of these Rhealstone components yields a set of time values. In order to perform overall comparisons between different real-time systems, the values have to be combined into a single Rhealstone performance number. The following steps are necessary to achieve a single Rhealstone number:

- 1. Express all measured time values in the same unit (seconds).

- 2. Compute the arithmetic mean of the different components.

- 3. Arithmetically invert the mean (from step 2), to obtain the number of Rhealstones per second.

[KAR90]

The calculated Rhealstone number treats all the Rhealstone components as equally important parameters of real-time performance. In other words, this number is good when evaluating a real-time system performance without a particular application in mind. When a real-time system is dedicated to a certain type of application, it is possible to calculate an *application-specific Rhealstone* number. This number is based on weighted components, i.e. each component is given unequal weights. For instance, an application may be interruptdriven and don not use semaphores at all. The steps for calculating application-specific Rhealstones are:

1. Estimate the relative frequency of each Rhealstone component's presence, and assign coefficients proportional to the frequencies.

2. Compute a weighted average of the Rhealstone components, and the invert it to get a result expressed in application-specific Rhealstones per second.

[KAR90]

For further details about computing application-specific Rhealstone numbers look in [KAR90], because in contains some improvements in comparison with the original proposal [KAR89].

#### Distributed Hartstone

Distributed Hartstone [KAM91] is an extension of the Hartstone benchmark [WEI90]. To be short the Hartstone benchmark is a benchmark aimed for realtime systems, which consists of 5 test series each with a synthetic workload aimed to test different task types.

The distributed Hartstone benchmark suite is developed for use in distributed realtime systems, and is well adopted to evaluate the performance of an RTOS. The distributed Hartstone benchmark as the Hartstone benchmark is based on a synthetic workload that represents the typical instruction stream of a scientific application. The benchmark consists of different task sets, which evaluates the performance of one particular feature each. In each task set, all factors are kept constant except one, which is the varied factor. The varied factor in a task set is typically an execution time or the number of task or messages, however the common factor is that the factors all can be increased to infinitely. In this way a distributed Hartstone benchmark always reaches the breaking point of the system, which is the point where the first deadline miss is experienced. In all the different tests with different task sets, it is the breaking point that yields the distributed Hartstone performance measure. The different task sets or measurements that forms the performance measure are:

• DSHcl Series: Communication latency

The end-to-end communication delay is measured, it is an important metric and we can all agree with that it is preferable to be able to distinguish between different systems in this area. A good system in this test should be able to provide a bounded worst-case time, and shortest possible delay to messages from high-prioritized tasks.

• DSHpq Series: Priority queuing

The scheduling of messages is tested; in ordinary systems it is often FIFO queues that handle the messages. But in a real-time system this is often not a suitable solution, since a high frequency or a fast activity cannot be delayed by an arbitrary number of other activities. This test is aimed to test if the message passing algorithms can avoid priority inversions and how successful the algorithm is on handling message priorities.

• DSNpp Series: Preemptability of the protocol engine If a low priority message is being handled by the protocol engine, this test is concerned about how long time it will take to switch over to an recently arrived high priority message.

- DScb Series: Communication bandwidth The communication bandwidth is a metric on how much traffic the communication medium can handle, included in this metric is also all the operating system processing required for communication.

- DSHmc Series: Media Contention This measure is concerned about the lower levels of the communication protocol. A suitable medium access protocol should provide a higher degree of service to high-prioritized messages. Even in the medium access layer priority inversion should be provided.

SSU

The Superconducting Super Collider Laboratory (SSCL) has made performancemeasurements on four different real-time kernels [ACH91]. The products were all from different vendors, but in order to compare and evaluate the different offerings, they were tested on the same hardware platform. The measurements falls into two categories: real-time and non real-time. The non real-time category contains the throughput measurements, including process creation/termination times, interprocess communication facilities involving messages, semaphores, shared memory and memory allocation/deallocation. Measurements classified as real-time, are for instance context switch times and interrupt latencies.

Each test was executed several times in order to compute the average time to complete a test. Then the entire measurement was repeated a number of times, to measure the minimum and maximum average values.

The different measurements that were performed are:

- 1. *Create/Delete task* This is the time it takes to create and delete a task. As soon a task I created, it deletes itself. The measurement includes two task context switches and the time it takes to create, start and delete a task.

- 2. *Ping suspend/resume task* A task with low priority resumes a suspended high priority task. The high priority task immediately suspends itself. This measurement includes two task context switches and the time it takes to suspend and resume a task.

- 3. *Suspend/Resume task* This test is identical to the previous test, except that this test does not include any task context switches, since in this test a high priority task suspends and resumes a suspended low priority task.

- 4. *Ping semaphore* Two tasks with equal priorities communicate with each other through semaphores, i.e. they are competing for a semaphore.

- 5. *Getting/Releasing semaphore* This test measure the time it takes to get and immediately release a semaphore within the same task context.

- 6. *Queue Fill, Drain, Fill Urgent* The time it takes to fill a queue and drain the queue is measured (two different tests). Then the tests are repeated with priority messages. The messages are sent to the head of the queue.

- 7. *Queue Fill/Drain* –A task sends a message to a queue, which the sending task immediately receives on the same queue. No task context switch will occur nor there is any pending queue operations. In other words, the time measured includes context switches, queue pends and sending and receiving a message.

- 8. *Allocating/Deallocating memory* This test measure the time it takes to allocate a number of buffers from a memory partition and the time it takes to return those buffers to the partition.

The conclusion that the authors of [ACH91] presented was that standards adherence makes code more portable. In order to perform measurements on the different kernels, they had to rewrite all the tests for all the kernels, because the interfaces were different. In other words, the tests were custom-written for each target platform.

# **Case Studies**

In this section some case studies of implemented multiprocessor real-time operating system kernels are presented. As introduction to this chapter our selection criteria's, and the used evaluation model are presented.

### **Selection criteria**

The overall requirements for the selected operating systems are support for realtime applications and multiprocessor management. The multiprocessor support should preferably be for NUMA or NORMA architectures, rather than only UMA systems. While no specific requirements of the real-time support are specified, it could be any mix between soft and hard real-time support, and anything the inventors of the operating system want to refer to as real-time.

In [BUT97], the authors divide current operating systems having real-time characteristics into three main categories, division (1):

- 1. Priority-based kernels for embedded applications

- 2. Real-time extended time-sharing operating systems

- 3. Research operating systems

Another division that exists is (2):

- 1. Commercial

- 2. Open source

- 3. Research

The selection of operating systems in this paper strives to cover both the listings above. An overview and classification of the studied operating systems are shown in table 1.

| RTOS                 | Classification   | Classification   |

|----------------------|------------------|------------------|

|                      | according to (1) | according to (2) |

| CHAOS <sup>arc</sup> | 3                | 3                |

| CHIMERA              | 3                | 3                |

| MARS                 | 3                | 3                |

| MontaVista Linux     | 2                | 1,2              |

| OSE                  | 1                | 1                |

| RT-MACH              | 2,3              | 3                |

| RTEMS                | 1                | 1,2              |

| SPRING               | 3                | 3                |

| SARA                 | 1,3              | 3                |

Table 1, RTOS classification table.

It is easy to conclude that the research operating systems are over-represented, but it is also these results and ideas that are most well described and include the most advanced solutions. Most of the information available for many commercial operating systems tend to be of more advertising nature, than honest descriptions on chosen algorithms and results. We have to make clear that the commercial RTOS we picked out, were selected because of the opposite. It was possible to find non-advertising documentation concerning OSE. On the other hand many of the published papers related to research operating systems, tend to describe only the parts that their research are focused on. In other words it is sometimes hard to get a general picture of a research system, but often easy to find results according to small special areas. Our responses to the documentation related to the open source operating systems is mixed. It was a lot of pages written, and it was possible to find what we searched for. But the really deep descriptions of methods and algorithms were missing; instead they referred to the actual code. The code describes everything, but it can be bothersome to understand the details.

Some commercial RTOS that are not investigated in this survey are VxWorks [WIN02], QNX [QNX02] and VRTX [MEN02]; all of them seem to be interesting. On the open source scene we have for instance not investigated eCos [RED02], a Linux distribution for real-time usage. The research systems we have left out include RK [LEE88], HARTIK [GBU93] and Asterix [THA01]. The reasons why we have not included the mentioned RTOS:es in the survey are for some RTOS:es limited multiprocessor support and concerning some other it has been hard to find relevant documentation. But the main reason is the need to limit the survey, due to the limited time a masters' thesis project contains.

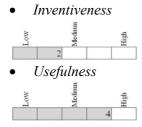

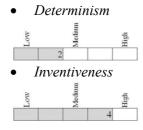

## **Evaluation model**

The chosen evaluation model, strives for the possibility that the readers themselves, shall be able to compare the different operating systems. An obvious way to achieve this goal is to evaluate many issues and then let the reader combine the issues freely. The studied issues will be: scheduling, memory management and interprocess communication. Each issue will be evaluated and graded from 1 to 5 according to the three keywords listed below, where 5 is the best. With this method, the result will be 3 grades for each operating system and studied issue.

- Determinism guarantee possibilities.

- Inventiveness extraordinary solutions.

- Usefulness typically flexibility or portability.

In this way the reader can create a lot of ranking orders, for instance it is possible to find the operating system with highest overall rank, or the operating system with the most deterministic scheduling algorithm, or the most useful interprocess communication methods. A summary of the evaluation is presented last in this chapter and, the motivations are presented in an evaluation section bounded to every investigated RTOS.

Examples of what we will reward can be found in the tables (2, 3 and 4) below for each issue and comparison keyword. Note that the listed examples in the tables

are only positive qualities; the absence or negation of the mentioned qualities will lead to a lower grade. A motivation to each assigned grade will be given.

| Category                        | Scheduling                                                             |  |

|---------------------------------|------------------------------------------------------------------------|--|

| (1)                             | WCET estimations possibilities.                                        |  |

|                                 | Off line analysis possibilities.                                       |  |

| (2)                             | Task placement algorithms.                                             |  |

|                                 | Multilevel scheduling.                                                 |  |

| (3)                             | Reasonable task attributes, (easy translation of real-world problems). |  |

|                                 | High potential CPU utilisation.                                        |  |

|                                 | Flexibility in the number of supported scheduling algorithms.          |  |

| Table 2, Scheduling evaluation. |                                                                        |  |

Category

Memory management

(1)

Bounded worst-case access time.

(2)

Virtual memory and dynamic allocation.

(2)

Cache support.

(3)

Dynamic and virtual memory.

Table 3, Memory management evaluation.

| Category | Interprocess Communication                           |  |

|----------|------------------------------------------------------|--|

| (1)      | Bounded worst-case transmission time.                |  |

|          | Resource reclaiming protocols.                       |  |

|          | Interrupt handling.                                  |  |

| (2)      | New or conceptually different methods.               |  |

| (3)      | Number of supported methods (message passing, shared |  |

|          | memory, remote procedure calls etc).                 |  |

|          | Potentially fast communication.                      |  |

|          | Interrupt handling.                                  |  |

Table 4, Interprocess Communication evaluation.

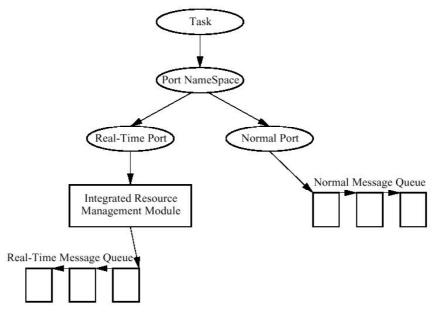

# **CHAOS**<sup>arc</sup>

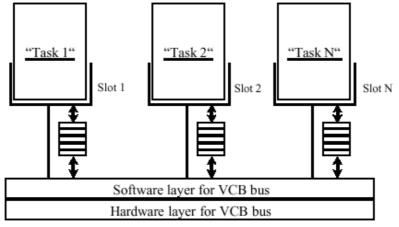

CHAOS<sup>arc</sup> [GHE93] is an object oriented real-time kernel of the CHAOS [SCH87] family. The CHAOS family of operating systems is structured in a layer model with three layers. The first layer or the layer closest to the hardware is CHAOS<sup>base</sup>, which is a machine dependent component that implements some basic operating system abstractions as threads, memory handling and synchronisation primitives. Above CHAOS<sup>base</sup> follows CHAOS<sup>min</sup>, in this layer the object-oriented approach is implemented with abstractions of classes, objects and invocations. In the top layer the policies of the different operating systems in the CHAOS family are implemented. The most interesting set of policies or operating system constructed with CHAOS<sup>base</sup> and CHAOS<sup>min</sup> are CHAOS<sup>arc</sup> according to the authors of [SCH90].

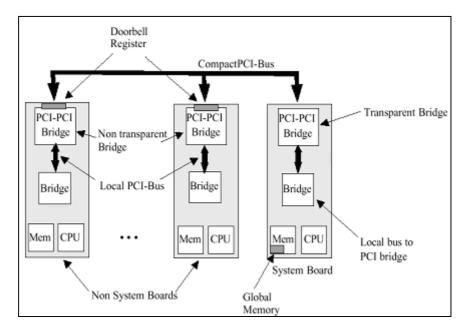

The hardware requirements of the operating system are dynamic since the hardware dependent module CHAOS<sup>base</sup> has been implemented or at least could be implemented on several different architectures. The implementation presented in this paper is running on a 32 node GP1000 BBN Butterfly [CRO85]. The Butterfly is a shared-memory parallel processor, with each processor node mainly consisting of a MC68020 processor, 4MB RAM and a co-processor called *Processor Node Controller* (PNC) which handles shared memory requests. The interconnection between processor nodes is a 32 Mbit/s per path multistage switch. The operating systems itself is running on every processor in the system.

The main contribution with CHAOS<sup>arc</sup> is the use of an object and class based environment for the programmer, when defining the application. Just as an object oriented language, CHAOS<sup>arc</sup> let the programmer define classes that represents a desired behaviour and the use of objects that is an instance of a class.

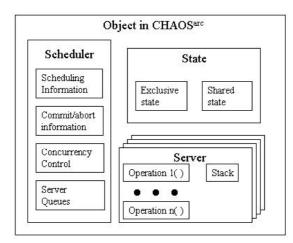

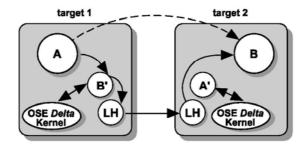

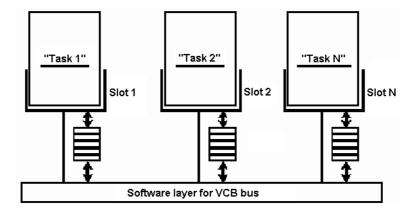

Four built in classes defines all primitive objects *Abstract Data Type* (ADT), *Threaded Abstract Data Type* (TADT), *monitor* and *task*. An ADT defines a passive object without execution threads or synchronization for concurrent calls. When calling an object of the ADT class, the method is executed in the address space of the caller and without synchronization of concurrent calls. When an object from the TADT class is called, a new execution thread without automatic synchronization of concurrent calls is created. A monitor is an object without execution threads that only allows one single call to be active at a time. Finally a task is an object with a single execution thread, all calls to a task are serialized and executed in the CHAOS<sup>min</sup> layer. But the CHAOS<sup>arc</sup> layer offers definition of more complex classes that are built upon these four primitive classes. A complex object can be represented as in figure 4, by a scheduler a state and a server.

Figure 4, Object representation in CHAOS<sup>arc</sup>.

The objects state is partitioned into a number of components, each of which can either be of shared or exclusive type. The shared component is directly accessible to all invocations of the same object, while an exclusive component is unique for every invocation of an object. But if the invocation commits the shared component is atomically copied back to the objects state, on the contrary when an invocation is aborted the result of exclusive components is discarded.

The objects scheduler receives and schedules all invocations to the object. The scheduling decisions by the objects scheduler is based on parameters passed with the invocation call (see section communication). The objects scheduling component is described in section scheduling.

The objects servers are simply threads that are able to execute any of the operations that the objects interface offers. Threads can either be created dynamically during run-time or static at object initialisation.

#### Scheduling

Multiprocessor scheduling is performed by the CHAOS<sup>arc</sup> policies. The policies can be configured different for every invocation of an operation and is carried out by the objects scheduler. The multiprocessor scheduling is performed in cooperation with the thread schedulers residing on every processor in the system. On this object level the processor placement of the task is determined. If the operation requires any locks the objects scheduler takes care of that problem, calculating times until locks can be achieved etc. Unfortunately the research around CHAOS<sup>arc</sup> was not focused on this type of multilevel scheduling (i.e., invocation scheduling followed by thread scheduling) so the exact algorithms used for the invocation scheduling were not described in detail.

The thread scheduling is distributed across the machine with one scheduler per processor. The scheduling algorithms [SCH89] basic data structure is a doubly linked list, called a slot list. The slot list records which threads have been scheduled during each of the time periods. The threads are preemptive scheduled with EDF (Earliest Deadline First)[LAY73], and as close to their start times as possible.

When a thread has to be scheduled, a feasibility test is performed. The test is a simple search for execution time. It starts with a slot compatible with the threads' start times, and ends at a slot compatible with the threads' deadline or when the total length of available time slots is equal to the threads execution time. If enough available time is found the thread is scheduled and the slot list is updated, else the thread is reported un-schedulable. The slot list can be accessed through a balanced binary tree; therefore a slot with a particular start time can be located in  $O(\log n)$  time.

Once a thread has passed the test and is going to be scheduled it has nothing to do with the slot list anymore. Instead all scheduled threads are put in another list and scheduled with EDF. This list includes all threads, even threads that have an earliest start time later than the current time. This is the reason why the list cannot be a queue, since the first thread might not have a feasible start time. So the final complexity of the feasibility test and the EDF scheduler is in the worst case reported to be  $O(n \log n)$ .

### Memory management

Memory management is described in [SCH87], because of the heavy use of dynamic memory during object creation and invocation; it is obvious that CHAOS<sup>arc</sup> needs some support for predictive dynamic memory. The solution is based on the observation that the possible memory requests are a finite set. The supported types of requests are:

- Status block's of known sizes, that the operating system uses to maintain an objects status during an invocation

- Parameter block's, which are used for parameter passing during an invocation

- Memory used for the representation of objects and processes