Version: 2005-09-27

### **MRTC Report**

### Component-Based Development of Safety-Critical Vehicular Systems

State of the Art, State of the Practice and Research Challenges

### Authors:

Ivica Crnkovic, Mälardalen University DeJiu Chen, Royal Institute of Technology Jad El-Khoury, Royal Institute of Technology Johan Fredriksson, Mälardalen University Hans Hansson, Mälardalen University Jörgen Hansson, Linköping University Joel, Huselius, Mälardalen University Ola Larses, Royal Institute of Technology Joakim Fröberg, Mälardalen University Mikael Nolin, Mälardalen University Thomas Nolte, Mälardalen University Christer Norström, Mälardalen University Kristian Sandström, Mälardalen University Aleksandra Tešanović, Linköping University Martin Törngren, Royal Institute of Technology Henrik Thane, Mälardalen University Simin Nadjm-Tehrani, Linköping University Mikael Åkerholm, Mälardalen University

> Editor: Ivica Crnkovic

### Chapter 2

### **Title: Vehicular Embedded Control Systems**

Authors: Martin Törngren, Ola Larses, Kristian Sandström, Johan Fredriksson, Joakim Fröberg, Christer Norström, Mikael Åkerholm

This chapter focuses on the state of practice of embedded control systems by describing existing software and hardware architectures. Compared to chapter one, this chapter provides more detail on the characteristics and constraints facing vehicular embedded systems. As a whole, the chapter lays a foundation for better understanding how the constraints and requirements of different vehicular systems have affected their architectures, thus forming a basis for the coming chapters. The chapter introduces basic concepts, terminology, fundamental structures of the control systems, and the context of the vehicular embedded systems; the mechanical environment, sensors and actuators. In later sections, current architectures of cars, heavy vehicles, trains and industrial robots are surveyed. The modeling and programming of these systems is further discussed in the following chapters. The chapter ends by summarizing current trends and challenges.

### 2.1 Fundamentals of embedded control systems

Since this chapter deals with embedded control systems it is appropriate to start out by defining and characterizing these two terms.

<u>An Embedded Computer Systems:</u> A computer system that is part of a larger system and performs some of the requirements of that system; for example, a computer system used in an aircraft or rapid transit system. (IEEE, 1992).

The area of embedded systems is very broad and spans a very large number of applications, from TV-sets, over mobile phones and toys, to production machinery, and system types, from single processor to distributed systems. Since all of these applications have very widely varying requirements it does not, in fact, make much sense to talk about embedded systems in general. However, turning to vehicular control systems does provide a useful delimitation. This leads us to the second definition.

<u>A control system</u>: A system in which a desired effect is achieved by operating on various inputs to the system until the output, which is a measure of the desired effect, falls within an acceptable range of values. (IEEE 1992

When implementing a control system today, a designer has a variety of technologies to choose from. For low-end products, analogue technology can be used. Today, however, digital technology is normally used and a typical implementation is based on a microcontroller; a highly integrated electronics device that includes a microprocessor, communication facilities, inputs (digital and analogue), and outputs (digital and analogue).

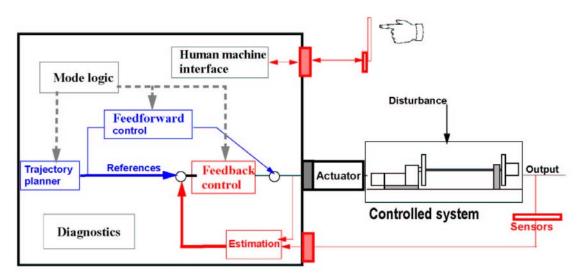

Embedded control system are in general characterized by the following (see also Fig. 1.4):

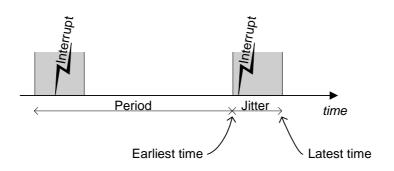

• *Feedback control:* This type of functionality matches the definition of a control system as given above. In vehicular systems, it is often the motion of the vehicle itself, or its various parts (e.g. the throttle) that is being controlled. Depending on if the setpoint to the controller is fixed, or varies frequently, the controller is called a regulator or a servo. Feedback has the important property that a certain robustness to

disturbances acting on the controlled process can be achieved. However, feedback controllers are sensitive to the timing induced in the feedback loop as a consequence of executing the controller. Discrete time control theory assumes equidistant sampling (i.e. none or negligible jitter) and negligible or constant feedback delays (this delay is counted between the time instants of sampling, and corresponding actuation actions), see e.g. Wittenmark et al. (1995), Åström and Wittenmark (1990).

- *Feedforward control*: Given knowledge of the controlled process, feedforward or open-loop control can be applied. In this case, no feedback is used which is like walking in a room without using any sensory feedback. This is only possibly with an accurate model of the controlled process. With such an accurate model, the required control signals to achieve a desired motion can be computed and applied to the actuators. In applications with well defined environments, such as in industrial robotics, feedforward control is used to a large extent. As no model is perfect, and since the controlled process may have characteristics that vary over-time, most control systems combine feedforward and feedback control.

- *Estimation:* Estimation can be used for several purposes including fusing information from several sensors to obtain better predictions of the system state, using models to predict certain states that can not be directly measured, or to detect a possible faulty behaviour of for example a braking system.

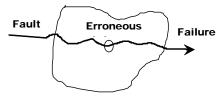

- *Mode logic (or arbitration):* Any non trivial control system will have several modes of operation, which may refer to initialisation, different operating conditions, and to graceful degradation. Consider for example a flight control system which has several air surfaces which are the actuators to be used for controlling the orientation (yaw, pitch and roll) of the aircraft. Given that one or more actuators begin to mal-function, the controller should hopefully detect this (see diagnostics below), and will then need to switch to another flight control law; this is necessary since there is now another aircraft in terms of dynamic behaviour to be controlled!

- *Diagnostics and logging:* For the purposes of on-line error detection, and for postmortem analysis (e.g. debugging) it is necessary to store the state of the control system. This state normally corresponds to the state variables used in the control design which typically includes measured variables (e.g. speed), estimated variables, and the control signal(s). Diagnostics usually refers to on-line analysis of the system state, for example to detect actuator malfunction or for that matter to communicate an upcoming service need to the driver, see e.g. Iserman (2002).

- *Tight coupling to the controlled process:* The tight coupling between the control system and the controlled process is manifested in several ways. Apart from aspects related to physical integration, sensing and actuation, the control system is also fundamentally related to the controlled process. Often, the control algorithms, synthesized from a validated model of the controlled system (model based control systems development). In other cases, the controller parameters are tuned with respect to the controlled process (e.g. the case for PID-controllers). Since the controlled process will change over time due to for example, it is usually necessary to either include adaption in the controller (such that controller parameters can be changed) or to make the controller robust enough to cope with changes in the controlled process. In addition, the speed (or bandwidth) of the closed loop system will provide requirements on the timing of the controller, including the sampling periods that successfully can be used, and feedback delays and jitter that can be allowed. These latter properties can

also be taken into account in the control design, however, providing a sort of a contract between the controller and its implementation.

- *Hierarchy and coordinating control:* Hierarchy is common in complex systems, and also in control systems. Humans have several low level controllers. One of them is located in the spine, and handles basic motion control such as walking. The brain contains several higher order controllers. Taking one example from vehicular systems, consider control of a car, where braking, engine and transmission controllers typically provide low (actuator) level control. The coordination of these is provided by higher level functions such as cruise and spin control. Along with the hierarchies normally follows an increased level of abstraction and slower time constants (frequencies).

- Autonomy and human control: Many control systems have an operator "in the loop". This is typical for vehicular systems, and the situation arises where conflicts can occur

who is deciding the motion of the vehicle at any given point in time? Careful analysis is required and special care has to be given to the human/machine interface.

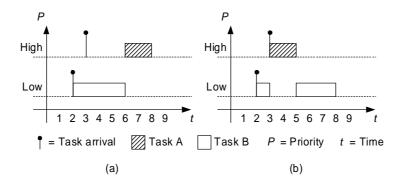

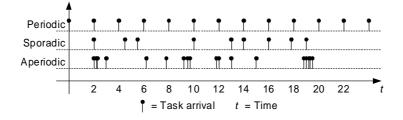

- *Time triggering and event triggering*: A typical control system includes activities which are both time- and event-triggered. In many cases, time-triggering follows naturally from the development of discrete time (sampled data) functions. Sometimes the controlled process is not discrete in time. This is the case for inherently sampled systems, one example being control of injection in a combustion engine; the point in time of injection depends on the speed and angular position of the engine parts, see e.g. Åström and Wittenmark (1990). Event-triggered functions thus include those who are inherently sampled and other functions who are not dictated or preferred to be implemented as periodic activities.

- *Safety related functionality:* Moving systems can be dangerous, vehicular control systems are therefore normally safety related. Not only is the control system required to operate reliably; the design of the system and its context must be carefully analysed to consider what might go wrong, and what the system should do in such cases. In safety critical control systems it is common to use diagnostics and analytical (model-based) redundancy both for detecting, and to some extent for handling errors. The robustness of control systems can also be utilized to handle certain failures.

Figure 2.1 Basic elements of a control system

As introduced in chapter one, a vehicle today contains several subsystems which usually are dedicated to different applications. One concrete example from the automotive industry is given in Figure 2.2. 1-X. Today, many of the exemplified functions have already been realized or are being developed (the latter is particularly valid for the safety, driver assistance and electrical power supply domains).

It follows from the above discussion that embedded control systems are populated with different functionality, and that this functionality has varying characteristics and requirements. Only a subset of the functions may for example be highly safety critical, the types of timing requirements vary, as will the computational models used for functions (e.g. discrete time equations vs. state machines). While the portions dedicated to motion control usually are associated with strict safety and timing requirements, these portions are typically relatively small compared to all other functionality.

| Powertrain and Chassis               | Safety                                | Driver Assistance                                       |

|--------------------------------------|---------------------------------------|---------------------------------------------------------|

| Gasoline direct injection            | Vehicle dynamic control               | Adaptive cruise control                                 |

| Active suspension control            | Occupant and rollover sensing         | Stop & go control                                       |

| On board diagnosis                   | Electro-mechanical/hydraulic<br>brake | Parking assistance, Parking brake by wire               |

| Combustion control                   | Collision warning and avoidance       | Blind spot detection                                    |

| Electromechanical valve lift control | Steer by wire, Brake by wire          | Video-based traffic sign, lane and obstacle recognition |

|                                      |                                       |                                                         |

| Body and comfort                     | Infotainment and Telematics           | Electrical Power supply                                 |

| Keyless Entry / Keyless Go           | Dynamic navigation                    | 14/42V power supply                                     |

| Lock by wire                         | Speech recognition                    | DC/DC converter                                         |

| Free programmable LC-display         | Multimedia entertainment              | Starter-Alternator                                      |

| Adaptive light distribution          | Internet access, E-mail               | Battery management                                      |

| Security systems                     | Telediagnosis                         | Alternator management                                   |

| Biometrical systems                  | Roadside assistance                   | Electrical load management                              |

*Figure 2.2 Trends on new functions as seen in the automotive industry in 1999.* (Source: Vehicle Body Electronics, Robert Bosch GmbH, Stuttgart, VDI Berichte 1999).

# 2.2 The context of vehicular embedded systems and distributed systems

The development of embedded control systems is strongly linked to the transformation of the traditional control systems to distributed control systems (today more fashionably called *by*-*wire* control) and to the embedding of the control systems into a quite harsh environment. In the following two subsections, the close relation to the vehicle (physical embedding) and the distributed system/functionality nature of embedded control systems are further elaborated.

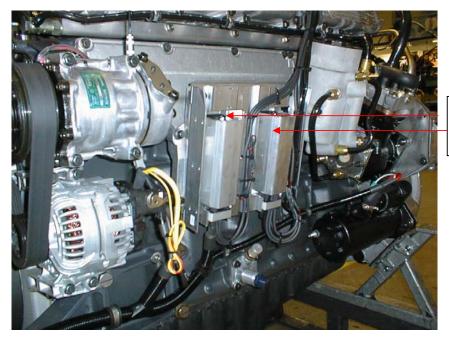

### 2.2.1 The mechanical environment: energy, sensors, actuators and information

In early implementations of engine controllers, the electronic control unit was usually mounted far from the engine. However, the resulting cabling and required connectors came to cause a number of problems. The need to transfer information from sensors using analogue signals a fairly long distance is not appropriate and requires costly cabling to handle the sensitivity of the signals. In addition, there is the need to reduce the number of connections. As a consequence, engine control units are today mounted directly on the engine, and in fact form a highly integrated part of the engine, see Figure 2.3 for an illustration of this.

The Scania diesel engine controller is designed to be mounted on the engine without cooling or damping. Special emphasis has been placed on the development of the connector to achieve robustness. The number of external connectors has been minimized; the only signal cabling to and from the engine goes through the ECU connectors. The engine ECU apart from engine control and CAN communication, carries out a number of additional functions such as controlling the fan, alternator, engine brake, turbo, and the EGR valve.

ECU connectors on top of the ECU

*Figure 2.3 Mechanical embedding exemplified by the Scania diesel engine controller (figure source from Scania)*

Although this type of physical embedding places high requirements on the physical design of the control unit to consider vibrations, varying temperature and humidity, it also provides a number of other benefits. The engine with its integrated ECU forms an intelligent component thus promotes modularisation. The ECU can be used for a variety of purposes such as providing component identity, individual component calibration, local control, and a means for integration with other control units.

The interfaces of such an intelligent actuator thus includes

- Energy supply (diesel in the example)

- Mechanical interfaces

- Information interface (CAN network)

- Energy supply for the ECU

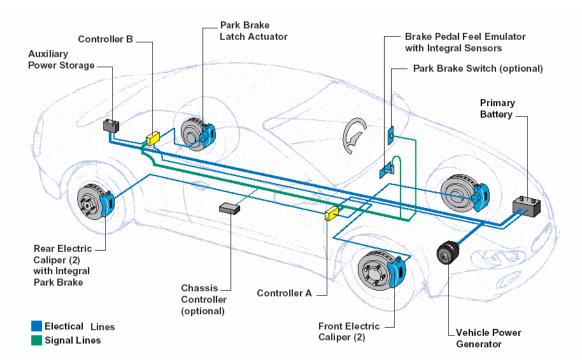

To further illustrate the context of an embedded control system, consider Figure 2.4.

*Figure 2.4* Mechanical embedding of a braking control system illustrating power supplies, power cabling, controllers, communication between controllers, and some sensor and actuator elements.

The following hardware components appear in Figure 2.4:

- Energy source(s) including a battery and a power generator, and there could of course be other sources or redundant specific sources.

- Energy distribution cabling referred to as electrical lines in Fig. 2.4, in terms of cabling for supplying various actuators and other energy users with energy.

- Actuators, for transforming energy into motion

- Sensors, to provide information to the control system and/or humans about the current status of the vehicle.

- Information distribution referred to as signal lines in Fig. 2.4, in a modern vehicle carried out by embedded networks such as the controller area network (CAN).

Note that since there are several actuators it may not be possible to run all actuators at once. Power management is essential in modern vehicles. For safety related functions, high requirements are placed on the reliability of all involved components. There may be inherent redundancy in the vehicle (for example true for the brakes but not for normal steering of a car).

### 2.2.2 Distributed control systems; towards by wire control

In general, there has over the last decades been a strong trend to connect stand-alone controllers by networks, forming distributed systems. The main driver for this has been cost reduction, since the use of networks makes reduction of the necessary cabling possible, or at least a possibility to bound the increase in length given the drastic increase in the number of control units. Another and closely related trend has been modularisation, where for example, an electronic control unit is physically integrated into an engine, forming a sort of mechatronic module. Combining the concepts of networks and mechatronic modules makes it

possible to reduce both the cabling and the number of connectors, the result of which is facilitated production and increased reliability.

A common definition of distributed systems is as follows:

Nodes part of a distributed system cooperate to accomplish a common goal.

This definition is of course quite general and there are many other definitions. A more fruitful approach is that of discussing how systems are distributed (or decentralized). A useful interpretation was introduced by Enslow who defined three dimensions of distribution according to which a system can be classified (Enslow, 1978). Clearly, there is a need for distributed hardware; but in addition, we may consider different distributions of data and of control (decisions) in the system.

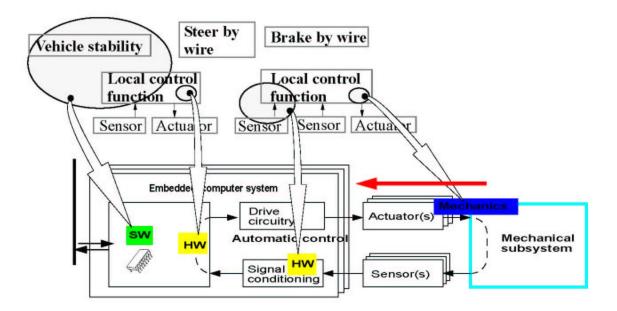

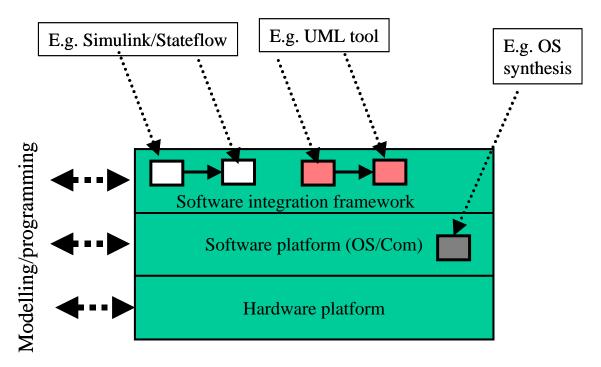

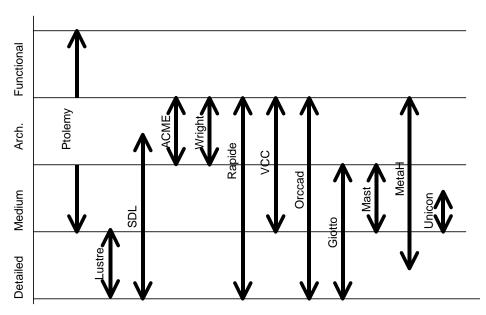

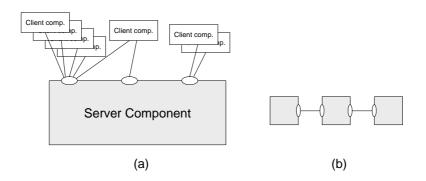

In essence, the concept of distributed systems then becomes that of mapping.; given a description of the system functionality (for example as illustrated by Figure 2.1), and the hardware architecture (for example as illustrated by Figure 2.4), we need to decide how to map the functions to the hardware components. This concept, where functions can be implemented by different technologies is illustrated in Figure 2.5.

## *Figure 2.5 Mapping of functionality to a hardware architecture including mechanical and electronic components, where the electronic components form a distributed computer system*

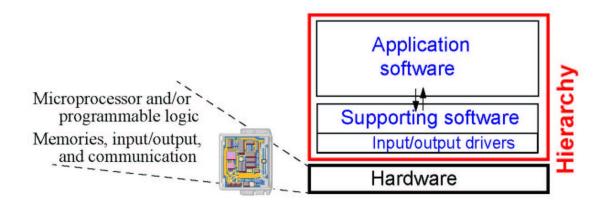

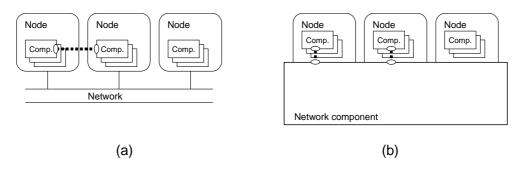

Each node of a distributed computer system is composed of hardware, supporting system software and application functions, as depicted in Figure 2.6. As described in section 2.1 we normally find hierarchies in the application. This is also true for the supporting software.

If we look in more detail on the mapping of the functions that are implemented in the distributed computer system, we find that there are in principle a wide variety of possibilities, ranging from a master-slave (often called distributed I/O) organization at the application, ranging to more fully distributed systems. Along with this mapping we also need to define or synthesize (see Törngren, 1995)

- the software architecture, including the partitioning of functions to tasks

- the execution strategy, referring to the choice of triggering, synchronization, and scheduling policies

• error detection and error handling strategies.

**Figure 2.6** Structure of a node, part of the embedded distributed computer system. The supporting software and the hardware are sometimes referred to as a platform. Note that Enslows classification applies equally well to all functions of the system, including the application and the system level

Introducing networks also means possibilities to more efficiently carry out diagnostics and to coordinate the operation of the separate systems, thus making new functionality possible. One example of this is the functionality provided by the Electronic Stability Program (ESP). ESP combines control of braking and throttle to implement yaw control to handle situations when a car is beginning to rotate (or spin) out of control for the driver. The technology uses a set of sensors connected to the braking and throttle system. Whenever the danger of a spin is detected, the ESP reacts by selectively applying braking force to the front and rear wheels and reducing or increasing engine torque. (Mercedes, 2003).

### 2.2.3 By wire control

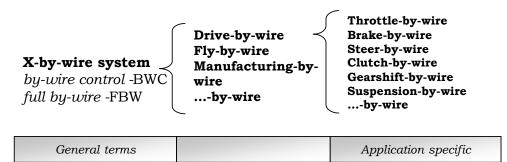

The term by-wire control is strongly related to distributed control systems. The terminology of by-wire systems has developed organically as new areas of coverage have been identified. We here suggest a structured approach to the terminology, see Larses (2003) for more on this topic. The by-wire terminology can principally be applied on any control system and in any area of application.

First a distinction between by-wire control systems and full by-wire systems need to be made. In a by-wire control system (BWC) some stage of the information transfer is performed through digital communication and digital decision making, not only analogue signals and filtering is used. It is generally assumed that the information or control signals are digitally communicated by an embedded control system. The embedded control system comprises of a set of electronic control units (ECU) that are interconnected in a local network. In a full bywire system (FBW) all the information is digital and also the power is transferred electrically by the use of electrical motors and electromechanical actuators. Using the terminology is it possible to state that a full by-wire system is a by-wire control system with electromechanical actuation.

A widely and rather informally used term is x-by-wire. X-by-wire is a general term that contains any application with by-wire functionality where 'x' is a referral to the actual application. The terminology refers to the application scope of the system and can be arranged hierarchically as shown in Figure 2.7. For example, the term fly-by-wire corresponds to applications in avionics and drive-by-wire covers automotive applications. Within these

categories further refinement is possible by naming specific functions like brake-by-wire and steer-by-wire.

### Figure 2.7 - By-wire terminology

All the different by-wire classes can obviously be of the type control system or full system, thus rendering the expression variants brake-by-wire control system and full brake-by-wire system. In a brake-by-wire control system is the information transfer from the brake pedal to the breaking actuator handled electronically but hydraulic or pneumatic actuators, probably with electronically controlled valves, perform the actuation. If the actuators are replaced with electrical motors a full brake-by-wire system is created.

By-wire control has been implemented for a long time and also applied to critical applications, most notably in terms of commercial fly-by-wire applications, which has been in use in the Airbus series aircraft since 1983 in the A310 model (Augustine, 2000). The Airbus 320 was the first that depends entirely on by-wire control and it was certified in 1988 (Briere & Traverse, 1993).

The introduction of by-wire systems have many benefits but also drawbacks. Cost and safety are two areas that have been pointed out as potential problem areas in the automotive industry (Feick et al, 2000). These, and similar, uncertainties have different impact in different by-wire application areas and give differences in the requirements on by-wire systems. That is, the requirements of manufacture-by-wire and fly-by-wire are significantly different due to inherent properties of the systems. These inherent properties can be described in three dimensions: The criticality or consequence of failures, the sensitivity to frequency of failure in operations and the cost sensitivity of an application, influences requirements as discussed in Chapter one.

Examples of rather early by-wire systems in the automotive industry include automated manual transmission (AMT). With AMT the mechanical connection to the transmission is eliminated and the gears can be chosen by pushing buttons or allowing a computer to run a gear selection program. AMT systems can be added onto existing manual systems and today exists in several cars like BMW, Mercedes-Benz, Alfa Romeo 156 and VW Lupo. The technology was first developed for motor sports to relieve the driver from using the clutch. (Wagner, 2003). AMT was introduced under the name Tiptronic by Porsche, ZF and Bosch on the Porsche 911 in 1989. Today several solutions are available like iShift from Volvo Trucks and Opticruise from Scania.

Several issues however hamper the introduction of steer by wire in vehicles in general including

- legislation

- user expectations

• cost-efficient embedded control. As discussed in Chapter one, the technological concepts used for by-wire systems in airplanes are not cost-efficient for the automotive industry.

In the automotive industry, full steer-by-wire is not available yet for the above mentioned reasons. However, several prototypes have been developed and intermediate solutions are being developed that typically include some form of mechanical back-up system. Steer-by-wire is commercially available in the form of Quadra-steer, four-wheel steering, from Delphi. This concept uses full steer by-wire for the steering of the rear wheels while using conventional steering on the front wheels. With four-wheel steering is possible to improve the turning radius of the vehicle when the front and rear wheel turn in opposite directions simultaneously. This is the case at low speeds, at high speeds the wheels steer in the same direction creating a sideways displacement of the vehicle without turning it, this functionality is intended for high speed highways improving lane shifting capabilities of the vehicle. (Amberkar et al, 2001).

### 2.3 Current architectures and standards

In this section we will present architectures, software technologies, and standards used today in vehicle electronic systems. The standards covered in this section are in several cases common within a domain whereas the architectures are specific for the companies that are represented.

### 2.3.1 Cars

Cars are typically manufactured in volumes in the order of millions per year. To achieve these volumes, and still offer the customer a wide range of choices, the products are built on platforms that contain common technology that has the flexibility to adapt to different kinds of cars. As an example, the Volvo XC90, which appeared in 2002, is based on the same platform as four previous Volvos launched since 1998.

The component technology is to a large extent provided by external suppliers, who work with many different car companies (or OEMs, original equipment manufacturers), providing similar parts. The role of the OEM is thus to provide specifications for the suppliers, so that the component will fit a particular car, and to integrate the components into a product. Traditionally, suppliers have developed physical parts, but in modern cars they also provide software. As the computational power of the electronic control units (ECUs) increase, it will be more common to include software from several suppliers in the same nodes, which increases the complexity of integration.

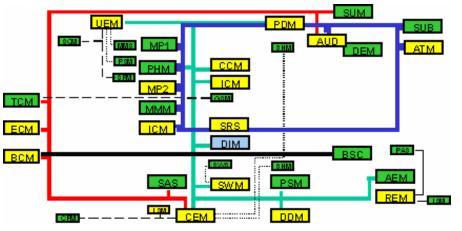

### System architecture

An example of a contemporary car electronic architecture is that of the Volvo XC90 (see *Figure 2.8.*). The boxes in the figure represent ECUs and the lines represent communication buses. The intent of the figure is to show the complexity rather than the details. The maximum configuration contains about 40 ECUs. They are connected mainly by two CAN networks, one for powertrain and one for body functionality. From some of the nodes, LIN sub networks are used to connect slave nodes into a subsystem. The other main structure is a MOST (MOST Specification Framework, 1999) Oring, connecting the infotainment nodes together, with a gateway to the CAN network for limited data exchange. Through this separation, the critical powertrain functions on the CAN network are protected from possible disturbances from the infotainment system. For more information about CAN and LIN see section 7.5.2. The diagnostics access to the entire car is via a single connection to one ECU. The figure shows approximately how the ECUs are placed in various locations in the car. The

partitioning of functionality is decided by the location of the sensors and actuators used, but also by the combinations of optional variants that are possible. If a car is sold with only a subset of the full functionality, the amount of physical hardware installed should be limited to the minimum necessary.

Figure 2.8. The electronic architecture of Volvo XC90.

### Node architecture

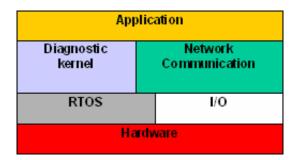

The current development trends in automotive software call for increasing standardization of the software structure in the nodes. In particular, the use of code generation requires a clear interface between the support software and the application, and the need to integrate software from different suppliers in the same node also calls for a well-defined structure. The node architecture (see Figure 2.9) includes several important components:

**Diagnostic kernels** provide an implementation of the diagnostic services that each node must implement to act as a client towards the off-board diagnostic tool. It relies on the communication software to access the networks and on the operating system to schedule diagnostic activities so that it does not interfere with the application functionality.

**Network communication software** provides a layer between the hardware and the application software, so that communication can be described at a high level of abstraction in the application, regardless of the low-level mechanisms employed to send data between the nodes. *Volcano* (Casparsson et. Al, 1998) Ois a communication concept used throughout the Volvo Car Corporation for managing network traffic. Currently Volcano supports the CAN and LIN busses. The basic concept in Volcano for communication between software components is signals, where a signal typically represents some engineering data. Through the Volcano API the underlying network technology is hidden from the application engineer. Moreover the engineer is not concerned with issues regarding assignment of signals to network frames. Instead this is done automatically ensuring signal timing requirements.

The Volcano concept also addresses vehicle manufacturer controlled integration of components developed by suppliers. This is done through the use of the Volcano API and by separate specification of the signals used by a component and the network configuration. The network configuration is provided by the integrator and specifies how signals are to be transferred over the network.

**Real-Time Operating Systems** (RTOS) provide services for task scheduling and synchronization. Traditional real-time operating systems are usually too resource consuming to be suitable for automotive applications, and do not provide the predictable timing that is needed. Therefore the new standard OSEK has been developed (OSEK/VDX OS 2.2, 2003). There are several suppliers of OSEK compliant operating systems.

Figure 2.9 The node architecture.

All these components interact with each other and with the application, and must therefore have standardized interfaces, and at the same time provide the required flexibility. To conserve hardware resources, the components are configurable to only include the parts that are really necessary in each particular instantiation.

For future system development, an important aspect is to create a more flexible software partitioning. The main use for this is probably not to find the optimal partitioning for each car on a given platform, since that would create too much work on the verification side, but to allow parts of the software to be reused from one platform to the next. This puts even higher demands on the node architecture, since the application must be totally independent from the hardware, through a standardized interface that is stable over time. Therefore, further standardization work is needed, in particular for sensor and actuator interfaces.

### 2.3.2 Construction Equipment

Volvo Construction Equipment, VCE, develops and manufactures a wide variety of construction equipment vehicles, such as articulated haulers, excavators, graders, backhoe loaders, and wheel loaders.

Compared with passenger cars, construction equipment vehicles are equipped with less complex electronic systems and networks. Also, the focus in product development is somewhat different. The products are to be used in construction sites, and the most important aspect of the vehicle is to provide a reliable machine to increase production.

In-vehicle electronic systems and networks are an important part of the construction equipment product and are crucial to provide end-user functionality, such as automatic gearbox, as well as providing diagnostic and service functions. Using a distributed electronic system also accommodates functions that reduce the cost of the vehicle e.g. reuse of sensors and displays, and adaptive solutions to accommodate cheaper mechanical parts.

### System architecture

The focus of VCE's electronic architecture effort is mainly concerned with assuring system properties including scalability to support product variation, reusability and partitioning of SW components to lower development cost, as well as safety and reliability. Moreover it is important to have an architecture that supports working with platforms.

VCE uses no externally developed vendor control units. This gives the possibility to use the same software component model, operating system, and reusing software components. By doing this, the partitioning of functionality is likely easier than in the case of a system with many differently developed control units. Easy partitioning gives the possibility to scale the system with respect to hardware and optimize hardware content in a specific product. For instance, a low-end product with fewer features requires less hardware resources, and can be

I/O

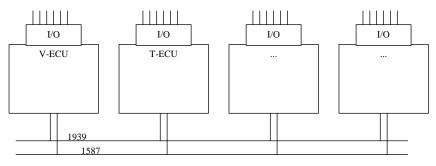

realized by placing software components on other nodes and thereby reduce the number of control units. This means that the number of control units can be chosen according to resource needs for a given configuration of a product. Thus, the architecture is reused, but the numbers of ECUs differ between products (see Figure 2.10).

Figure 2.10 VCE Network Architecture

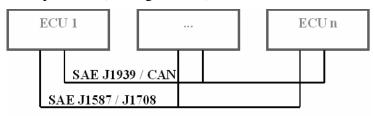

In the domain of heavy vehicles, the *SAE J1939* standard (SAE Standard, SAE J1939) Ofor communication between components has been created by a number of vehicle manufacturers and sub suppliers. SAE J1939 uses CAN for communication and defines a transport service in the network layer. In the application layer the protocol defines data (signals e.g. vehicle speed) and the packaging of signals in frames. Moreover, J1939 also define the interaction between components, e.g. the interaction between engine and transmission during gear shifting. To provide for vehicle manufacturer specific functionality the protocol also allows some proprietary messages.

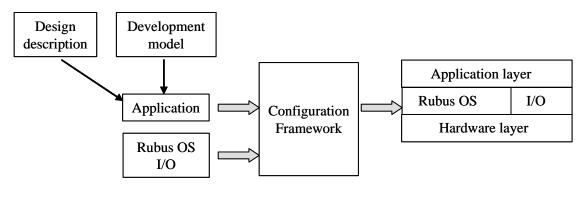

### Node architecture

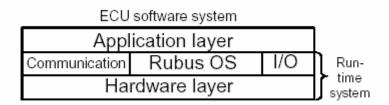

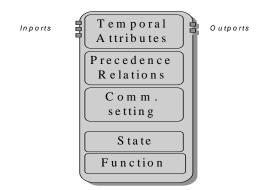

As depicted in Figure 2.11, each ECU consists of hardware and two different software layers (Nyström et.al, 2002)0. The top layer is an application layer with specific functionality for different ECU's and products. The middle layers are the interfaces between the application and the hardware. These layers are the communication layer, which handles communication between different nodes, the I/O layer that handles the in and output on the affected node and the real-time operating system Rubus, which handles task scheduling and synchronization.

### Figure 2.11 The Node (ECU) Architecture

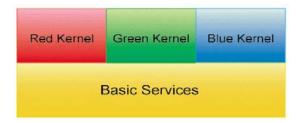

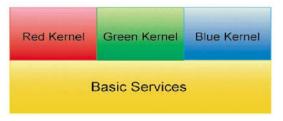

A view of the Rubus RTOS used by Volvo Construction is shown in Figure 2.12. Rubus is a real-time operating system with support for both static scheduling and pre-emptive fixed priority scheduling. The static and pre-emptive fixed priority schedulers are referred to as the *red* and *blue* parts of Rubus respectively. The red part only handles hard, static real-time, while the blue part only handles soft real-time. Finally, there is also a green part of Rubus, which is an interrupt handler kernel. It has the highest priority, and distributes and routes the interrupts.

The red part of Rubus always has higher priority than the blue part. Therefore, the red part is used for time critical operations (firm and hard real-time), since it is easier to verify timing properties of the red part. The blue part of Rubus is usually used for more dynamic properties, and soft real-time. The green part always handles all interrupts, and has the highest priority in the system.

Figure 2.12 Rubus RTOS Architecture

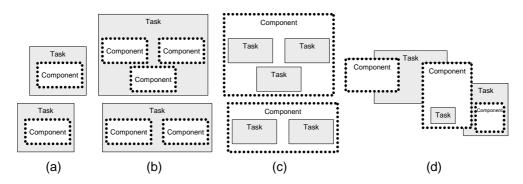

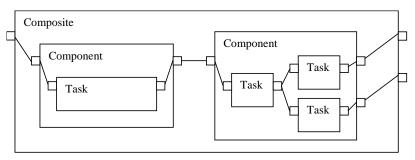

### Component model

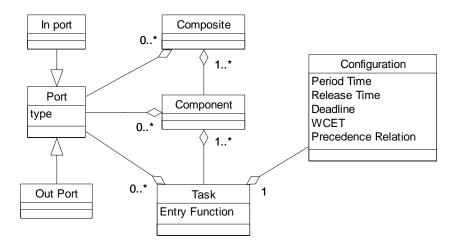

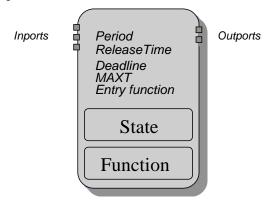

Volvo uses the Rubus component model. A component in that model consists of one or more tasks, which are the run-time entities executed by the operating system. A task in turn is defined by a function pointer, data ports, and some attributes building the current configuration of the task. We can also identify a composite, which is a logical composition of one or more components. Components and composites are technically the same, but an encapsulation of components is logically separated from an encapsulation of tasks by different notions. For a more detailed description of the Rubus component model see section 4.4.3.

### 2.3.3 Trains

We will have a closer look into systems manufactured by Bombardier Transportation, which is a train manufacturer, with a wide range of products. Some samples from their product line are passenger rail vehicles, total transit systems, locomotives, freight cars, propulsion and controls, and signaling equipment.

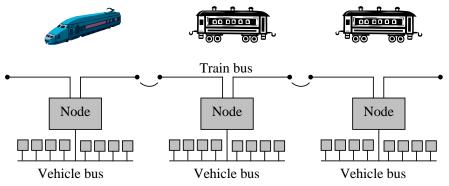

### System architecture

Bombardier designates the distributed control system Mitrac, and the heart of the system is the *Train Communication Network* (TCN) (Kirrmann et.al, 2001) that defines standards for a data communication network, interconnecting devices both between and within rail vehicles. The TCN is adopted as a standard by both IEC (IEC std. 61375) and IEEE (IEEE std. 1473). The general architecture is shown in Figure 2.13 from (Kirrmann et.al, 2001). Each vehicle has an own vehicle bus connecting on board devices, such as sensors and actuators for doors, brakes and air condition system. Applications which exchange information cannot determine whether its peer resides on the same bus, train or anywhere else in the network. From the train bus view the internal organization of a node is not detectable, since each vehicle bus is treated as an own node on the train bus.

Figure 2.13, the train communication network

The bus architecture is divided into a WTB interconnecting all vehicles, and in each vehicle a MVB, as according to the TCN standard. On each MVB there is between 5-10 processors. It is also common that the MVB actually consists of several buses, since the drive line

consisting of for instance anti spin and brake system often is separated from ordinary vehicle control functionality as door opening, air conditioning and entertainment system. For further details on the Train communication network see section 7.5.2.

### Node architecture

A physical node in a control system either belongs to the drive line or to the ordinary vehicle control. A node belonging to the driveline is slightly more advanced, both types of nodes are based on the M360 board, but drive line nodes often has an additional Field Programmable Gate Array (FPGA) and more I/O units. The FPGA is used for tasks with high performance demands.

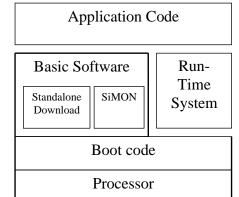

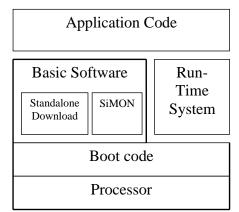

Each node in the system has approximately between 0.5 to 4 MB binary application code. It is roughly organized as in Figure 2.14. The three main parts are as shown in the figure basic software, run-time system, and application code. The basic software and run-time system is together denoted Common Software Structures (CSS), which is the basic platform, e.g., the operating system. The basic software in turn includes the three components Bootcode, SiMon and Standalone Download. These three components are downloaded to the node during the hardware manufacturing process and are consequently already in the node when it is delivered from the factory. Another part is the run-time system, which can be further decomposed:

- Run-time system starter, is initialization and start-up routines.

- Run-time services, implemented by the operating system.

- Underlying real-time kernel, which is the third party kernel VxWorks.

Eventually, the application code which utilizes the underlying layers are situated on top in the figure.

Figure 2.14. A rough decomposition of a typical node

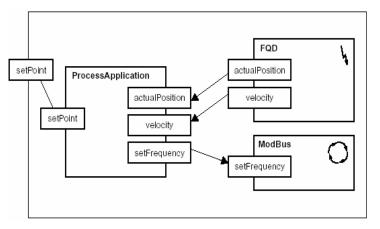

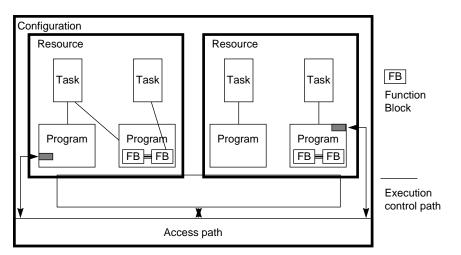

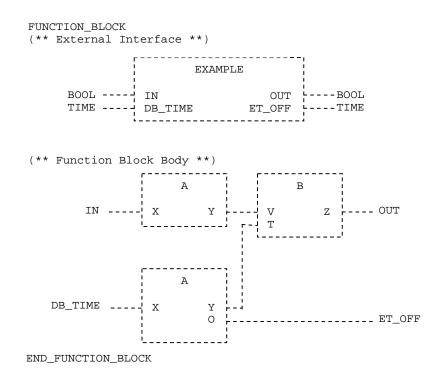

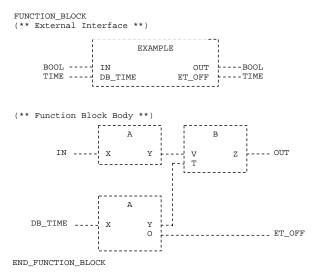

Bombardier uses the programming languages defined in the IEC 61131-3 standard, for programming their devices. The primary language used is the graphical language called function blocks, although the standard defines three graphical and two textual programming languages.

The basics of the language are that an application is divided into a number of function blocks. Each function block has a set of in and out ports, and a hidden internal implementation. Each function block can contain both data and an implementation as a function. The intention with the function blocks is that they should be equivalent to integrated circuits, representing a specialized control function. The external data interface of a function block is ports and the function block implements one single function. Ports are either in or out ports, and have a type and a name. For a more detailed description of the IEC61131-3 Function block diagrams see section 4.4.6.

### 2.3.4 Industrial robotics

Industrial robots are typically manufactured in volumes of 10 thousands per year for the leading manufactures. That figure includes different kinds of robots. To make the manufacturing of the control system cost efficient, the same controller type is often used for different kinds of robots. Therefore, the control system has to be configurable to a large extent.

The core part of a robot system is the motion control, the application packages (welding, assembling, etc) and the way to programming the robot. Several other parts like I/O and communication protocols are provided by suppliers in many cases. Therefore, the system has to be open to enable easy integration of for example new communication protocols. Hardware is also provided by suppliers. Since the software will survive many versions of hardware, the software has to be easy to port.

From the users' point of view, the reliability is the single most important property. Today the mean time between failure (MTBF) is required to be greater than 60000 h.

Industrial robots are most often part of a larger system, e.g. an assembly line for cars, which includes PLC systems and production systems from other vendors. Therefore, each robot manufacturer has to fulfil the communication standards set by that specific customer. Consequently, all robot manufacturers have to fulfil several field bus protocols e.g., several variants of Profibus, Interbus, Foundation fieldbus, FIP, etc. Several of these protocols are described in Section 7.5.2.

### System architecture

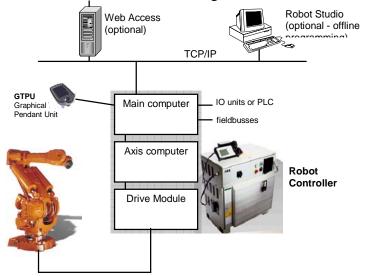

The specific architecture we will look into is the ABB Robotics control system S4. This control system was initially developed in the beginning of the nineties.

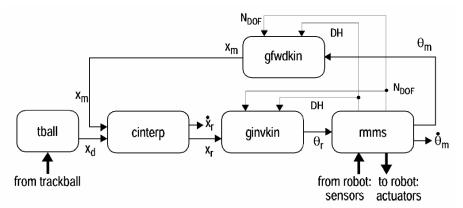

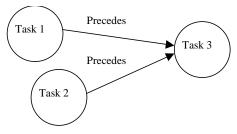

Each robot contains three closely connected nodes, a main node that generates the path to follow, the axis node, which controls each axis of the robot, and finally the I/O node, which interacts with external sensors and actuators, see Figure 2.15.

Figure 2.15 The system architecture of a robot controller.

### Node architecture

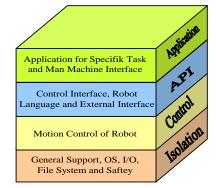

ABB Robotics uses an object oriented approach, although most of the code is written in the imperative C-language. The controller consists of approximately 2 500 KLOC divided on

400-500 components organized in 15 subsystems. The software architecture is divided into a number of major components

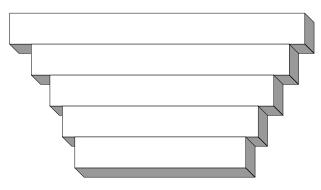

Somewhat simplified each major component represent a subject area in the organization, which is responsible for that particular component. The static software architecture can ideally be visualized as a layered architecture shown in Figure 2.16. The layers are:

- an application layer,

- a high level application programming language layer,

- a core control layer, and

- a platform isolation layer.

Starting from the lowest level, the isolation layer is a general supporting layer, which implements I/O and file system routines. But also interfaces to the operating system to decouple the rest of the application from operating system internals, the operating system can be either VxWorks for the real controller or a Windows platform for a simulation application.

The second layer is the control layer, which controls the motion control of the robot. Next layer is the high level application programming layer, and it contains some sub layers and subject areas. It contains controller interfaces and external interfaces, which provide interfaces to the lower levels in the hierarchy, for access from higher levels or from external components. It also contains the robot language layer, which implements the RAPID language. Highest in the hierarchy the application layer contain the application designed for each robots particular task, it also deals with man and machine interaction.

Figure 2.16 Idealized static system architecture

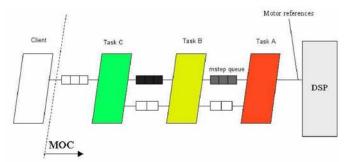

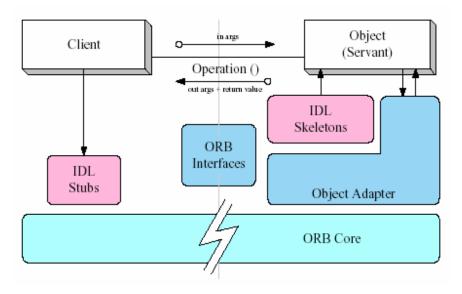

The execution model is described as event driven, built around an internal software based inter-process communication bus. The inter process communication model is based on the analogy of a parallel HW bus like the VME-bus, where the bus has a finite number of free slots for boards. A task in the system can be seen as a board that is connected to the bus via one of the available slots, see Figure 2.17.

Figure 2.17. The main on-line events are processed on the virtual communication bus

The success of this approach is that the control system has been ported several times, from Motorola based architecture to Intel based architecture. Further, the simulation tools run the same software as the real controller.

The main challenge in the future is to move one step further in openness. To allow third parties to add their specific application add on. To open the controller for third party is technically easy, but to still guarantee an MTBF on 60000 h is the challenge.

### 2.4 Conclusion

The development of vehicles is going through a dramatic evolution, in their transitioning from pure mechanical devices to mechatronic machines. It is today stated by Daimler Chrysler that 90% of the innovation in the automotive lies in electronics and software. The evolution is mirrored by the fact that mechatronic modules are appearing, for example, an engine with integrated control unit.

Vehicular embedded control systems are challenging applications that have parts that are safety related, come along with a variety of real-time requirements, and that are tightly related to the process they are controlling. The control systems are increasingly being implemented in distributed computer systems and require a multitude of competencies to be developed to meet quality requirements in a cost-efficient way.

In vehicles, embedded control systems have grown from stand-alone controllers to distributed control systems. The growth has been "bottom-up" in nature. The results is that of a sudden increase in both possibilities and interaction problems. The resulting complexity is illustrated by Figures 2.1, 2.4, 2.8 and so on, showing a number of structures (mechanical, electronics hardware, software, and functional) and indicating intricate relations among them.

Standardized hardware and software platforms are emerging for aeroplanes, but for other vehicles, it is only the networks that have been standardized. Consequently, the main component used in todays embedded control systems is that of the "electronic control unit" – a complete hardware node. This today means that adding a new function is very often translated into adding a new node to a system that incorporates this functionality.

Complexity arises also in the development of these systems, and this stems not only from the product complexity, but also from the complexity of the involved organizations; a vehicle is composed of hardware components coming from a multitude of companies. It is not uncommon that a car manufacturer today in-house only develops a few control units – a very low percentage of some 70 control units indeed. This means that system integrators in some cases are trying to regain control and development of the control units because of their large impact on the vehicle. Systems integration is complicated by the fact that manual specifications are used, leaving room for misinterpretations, causing costly iterations, and highly difficult systems integration.

A number of challenges lies ahead for the development of such systems:

- Systems integration is today a central problem in development. Well defined architectures and standards are here expected to improve the situation.

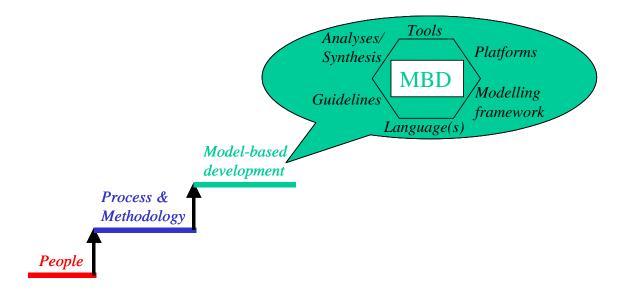

- Model based development (MBD) is seen as a necessary technology, to master both the product and the development complexity. However, while MBD is practiced for subsystems, there is no holistic MBD available yet, and there are plenty of research and industrial efforts trying to develop MBD further, see e.g. Artist (2003).

- The architectures needs to take several dependability aspects into account, including safety, reliability and security. The physical integration, and both information and energy flows are here essential to consider.

- Extending the hardware oriented component approach to software components; There are several efforts striving for software component based development (see e.g. East-EAA, 2003).

- The balance in automation needs to be carefully considered. To this end, better modelling and analysis of human machine interactions is required.

### References

Amberkar S, Czerny B, D'Ambrosio J, Demerly J & Murray B. 2001. A Comprehensive Hazard analysis technique for safety-critical automotive systems. SAE 2001 World Congress. Detroit, Michigan. March 5-8, 2001 SAE 2001-01-0674.

Artist (2003). Artist roadmap on Hard Real-time Systems: http://www.systemes-critiques.org/ARTIST/Roadmaps/A1-roadmap.pdf

- Åström, K. J. and Wittenmark B., Computer-Controlled Systems, Theory and Design. Second edition, Prentice-Hall International, inc, 1990, ISBN 0-13-172784-2.

- Augustine N R. 2000. Today... Tomorrow... of multidisciplinary systems of systems. IEEE Aerospace and Electronics Systems Magazine. Vol 15. No 10. October 2000. p 137– 144.

- Briere D & Traverse P. 1993. AIRBUS A320/A330/A340 Electrical Flight Controls: A Family of Fault-Tolerant Systems. Digest of Papers, The Twenty-Third International Symposium on Fault-Tolerant Computing. August 1993

Casparsson (1998) L. Casparsson, A. Rajnak, K. Tindell, and P. Malmberg, *Volcano a revolution in on-board communications*, Volvo Technology Report. December 1998.

- EAST-EAA. East-EAA an ITEA project: http://www.east-eea.net/

- Enslow P.H, 1978. What is a distributed system?. Computer, January 1978, pp. 13-21.

- Feick S, Pandit M, Zimmer M & Uhler R. 2000. Steer-by-Wire as a Mechatronic Implementation. SAE 2000 World Congress. Detroit, MI. March 6-9. 2000. SAE 2000-01-0823.

- IEEE (1992). The new IEEE standard dictionary of electrical and electronics terms. IEEE std. 100-1992. 5<sup>th</sup> edition.

- Isermann (2002). Rolf Isermann et al. Fault-tolerant driv by wire systems. IEEE Control Systems. October 2002, Vol. 22, No. 5.

Kirrmann (2001). H. Kirrmann and P. A. Zuber, The IEC/IEEE Train Communication Network, IEEE Micro, March-April 2001, pages 81-92.

- Larses (2003). Ola Larses. Dependable architectures for automotive electronics; Philosophy, Theory and Practice. PhD thesis, Division of Mechatronics, Dept. of Machine Design, Royal Institute of Technology, Stockholm, Sweden.

- Mercedes. 2003. Innovation Research & Technology. www.mercedes.com/e/innovation/rd/ accessed 2003-01-20.

MOST (1999). MOST Specification Framework Rev 1.1, MOST Cooperation, www.mostnet.de, November 1999.

Nyström (2002). Dag Nyström, Aleksandra Tesanovic, Christer Norström, Jörgen Hansson, and Nils-Erik Bånkestad, Data Management Issues in Vehicle Control Systems: a Case Study, In Euromicro Real-Time Conference 2002, June 2002.

OSEK/VDX OS 2.2, http://www.osek-vdx.org

SAE Standard, SAE J1939 Standards Collection, www.sae.org

- Törngren (1995). Martin Törngren. Modelling and design of distributed real-time control applications. Doctoral thesis, Dept. of Machine Design, KTH, ISSN1400-1179, ISRN KTH/MMK--95/7--SE.

- Wagner G. 2003. Transmission options. SAE Automotive Engineering Online. www.sae.org/automag/features/transopt/ accessed 2003-01-20.

Wittenmark Björn, Nilsson Johan and Törngren Martin (1995). Timing Problems in Real-time Control Systems: Problem Formulation. American Control Conference, June 1995, Seattle, Washington.

### Chapter 3 System and Software Life Cycle Process

Ivica Crnkovic, Mikael Åkerholm, Johan Fredriksson, Christer Norström

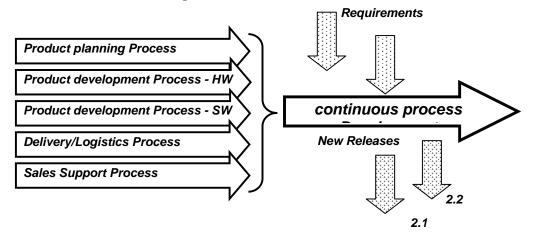

The chapter givens an introduction to system and software life cycle processes with focus on software development. In particular component-based approach and model-based development are addressed. The chapter discusses the advantages and disadvantages of these approaches and a possibility of their combination. The state of practice is illustrated by several case studies. Finally, the chapter summarizes the challenges and needs for further research in the domain of system and software development when applying component-based approach.

### 3.1 Introduction

By a system life cycle we mean all activities related to a system during its entire life: A system life cycle starts with its initiation by appearance of ideas for its development, goes true its development process, and later its delivery, maintenance and support and ends with a disposal of the system. Although the support and maintenance phase for most of systems occupies a majority of time and costs, the development phase has been in focus of research communities and main concerns in industry. The increasing maintenance costs and a need for adoption of existing products to new requirements and new environments emphasize a need for methods and technologies that support continuous evolvement of products. This is in particular for software systems or computer-based systems. New technologies such as component-based development and model-based development focus on shorter development cycles and on provide better prerequisite for efficient maintenance. However these approaches require processes that differ from traditional approaches. In these chapters we summarize the basic characteristics of these processes and discuss whether these processes are feasible for development on embedded systems. To show complexity in development and maintenance of safety-critical development systems the chapter gives overviews of several cases studies - from automotive and train industry.

### 3.2 System, software and hardware life cycles

### 3.2.1 System Lifecycle

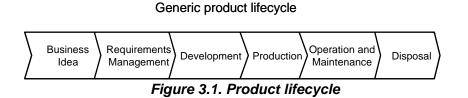

Many products have a long life, of which the "normal" user (so called end user) only sees a small fraction. To be aware of an "entire life" of a product we must understand all the processes involved in the product's development and operation, and of all activities of the people involved in the processes. The mechanism used to structure these processes and to identify the major activities is called a *system life cycle mode* or *product life cycle*. A system lifecycle is divided in different phases. Each phase is characterized by its inputs, results, its activities, support provided, the roles of the different people involved in the activities and the different technologies and techniques used in them. Independent of the product type, we can identify six generic phases [CR03]: the business idea of the product, requirements management, development, production, operation and maintenance, and finally disposal (see Figure 3.1).

The *business idea* phase begins with a perception for a new product. It continues with an assessment of the market and technology and with the identification of the key requirements of the product. At this stage a feasibility study is performed; e.g. all available information is collected and with this as a basis it is decided if it is feasible to develop the product.

The *requirements management* phase focuses on a further identification of requirements, their analysis and their specification. The result of this phase is a product requirements specification.

The next phase, *development*, includes design and implementation activities. The result from this phase is the implementation of all the artifacts needed for production.

The *production* phase (also called manufacturing phase) is significantly different for software and hardware products. In the case of pure software products, this phase is automated to a high degree and has very low costs in comparison with the other phases; as an absolute minimum it becomes a matter of only downloading the software product. On the other hand, for a product with hardware elements this is probably the most demanding and the most costly of all the phases. Therefore, for hardware products, much effort is invested in coping with the production requirements and in keeping production costs low.

*Operation and maintenance* is the phase in which the product is used by consumers, and often the only phase they will see. To ensure correct operation, the product may require continuous support and maintenance.

The final phase of the lifecycle of a product is its *disposal*. The significance of this phase depends very much on the product. Different aspects not related to the product itself but to its surroundings must be taken into consideration; for example its impact on the environment, the question of its replacement etc.

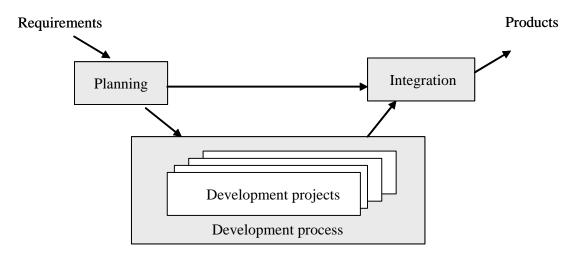

### 3.2.2 The Development Phase

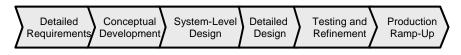

Generic system lifecycle models can be implemented in different ways. There will be particular differences in the cases of software and hardware products. To describe the main steps of pure hardware development, we can adopt a generic development process from Ulrich and Eppinger [CR03] in which the process contains six steps, as depicted in Figure 3.2 (the lower part). The development phase is preceded by *the detailed requirements management*. A detailed requirement solicitation and specification is closely connected to the development, in particular to the *conceptual development* in which the product concepts are generated. At the *system-level design*, the architecture of the product is decided, this including the identification of sub-systems and components. The components are further designed during the *detailed design*. *Testing and refinement* includes the building of product prototypes to test both the product and the production system. During the *production ramp-up*, the production system is used for serial production of the product, beginning at a low rate, but then increasing to full production.

The software development process consists of similar phases, expressed in a most illustrative way in the Waterfall model, shown in Figure 1.3 (the upper part). The model includes the following phases: Requirements analysis, design (overall and detailed), implementation, integration and test, and finally release. The *detailed requirements* analysis phase is completed with a requirements specification. This specification is an input to the system *design* which consists of two steps; the overall design where the system architecture is designed, the components and their interfaces are identified, and the detailed design in which the component implementations are specified. In the *implementation* phase the developers follow the design documentation and implement the system in the form of algorithms and data structures specified and written in different programming languages. In the *integration and system test* phase, the integrators build the system from the components. The system is then ready for the system test. The final development phase in this model is the *release* management in which the product is packaged in an appropriate form for delivery and installation at the customer's premises.

Hardware Development

Figure 3.2. Software and hardware development processes

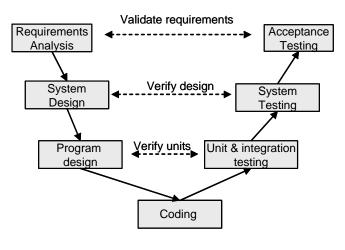

The waterfall model rests on the notion that it is possible to define and describe all the system requirements and software features beforehand, or at least very early in the development process. This model has an important place in software engineering. It provides a template into which methods for analysis, design, implementation, integration, verification, validation, and maintenance can be placed and clearly localized. Although in practice never used in its pure (and rather naïve) form, the sequential model has remained as the most influential software development process model. For example, the waterfall model in combination with prototyping, or V-model [So01] has been extensively used for the entire lifecycle or as a part of other models, covering particular phases of the entire process model. In particular V-model which connects specification with verification and validation phases is an established procedure in safety-critical domains. V-model is shown of figure 3.3.

Figure 3.3. V model

Both waterfall and V-model belong to a category of sequential development processes. A sequential model requires a complete specification of requirements and there can therefore be difficulty in accommodating the natural uncertainty that exists at the beginning of many projects. It is also difficult to add or change requirements during the development, as, once performed, activities are regarded as completed. In practice, requirements will change and new features will be called for and a purely sequential approach to software development can be difficult and in many cases unsatisfactory. For this and other reasons there exists other approaches. Examples of these are evolutionary approaches: incremental, iterative or spiral development.

An important question is which development processes are feasible and which apropriate for component-based approach or for the model-based approach

### 3.3 Component-based Development Processes

Component-based approach specifically focuses on questions related to components and in that sense it distinguishes the process of "component development" from that of "system development with components". There is a difference in requirements and business ideas in these two cases and different approaches are necessary. Components are built to be used and reused in many applications, some possibly not yet existing, in some possibly unforeseen way. A component must be well specified, easy to understand, sufficiently general, easy to adapt, easy to deliver and deploy and easy to replace. The component interface must be as simple as possible and when used strictly separated (both physically and logically) from its implementation. On the other hand a complete specification of a component must include not only information about which services it provides but also which services and resources it requires, as well as information about other properties – this being especially true for real-time components. These requirements increase the efforts needed for the component development. According to certain experience [CL00] building a reusable component takes at least three times more efforts that building software with the same functionality but not as an reusable unit. System development with components is focused on the identification of reusable entities and relations between them, beginning from the system requirements and from the availability of components already developed [CL02]. Much implementation effort in system development will no longer be necessary but the effort required in dealing with components; locating them, selecting those most appropriate, testing them, etc. will increase [MO00].

We not only recognize different activities in the two processes, but also find that many of these activities can be performed independently of each other. In reality the processes are already separate as many components are developed by third parties, independently of system development. Even components being developed internally in an organization which uses these very same components, are often treated as separate entities developed separately.

The separation of development of components from systems has severe implications. The understanding of the components must be sufficient to successfully build the systems without looking in component internals (for example source code). A component is treated as a black box, with an extensive specification. The specification must be able to specify all properties of the component required in the system building process. Further, it must be possible to verify these properties. These facts have implications on development processes, development of systems and development of components. The sections below describe theses processes in more details.

### 3.3.1 Component-Based System Development Lifecycle

Development with components is focused on the identification of reusable entities and relations between them, starting from the system requirements. The early design process includes two essential steps: Firstly, specification of system architecture in terms of functional components and their interaction, this giving a logical view of the systems and secondly, specification of a system architecture consisting of physical components. In many domains, in particular those with large volumes and many variations, principles of product-line architecture are applied. The basic characteristic of this approach is to maintain a basic architecture and obtain variability by integration of different components, or different component variants.

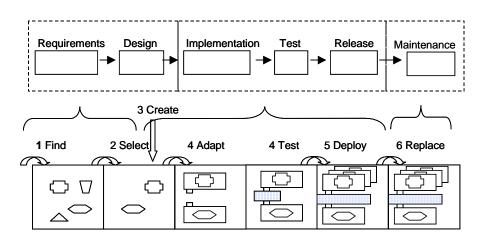

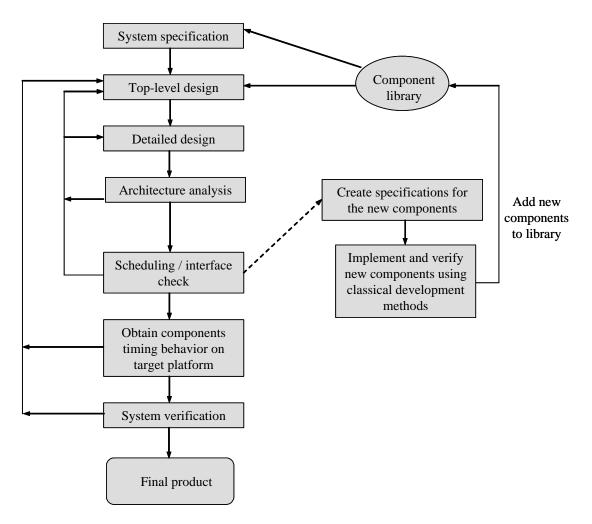

Different lifecycle models, established in software engineering, can be used in the system development process. These models can be modified to emphasize component-centric activities. Let us, consider, for example, the waterfall model using an extreme component-based approach. Figure 3.1 shows the waterfall model. Identifying requirements and a design in the waterfall process is combined with finding and selecting components. The design includes the system architecture design and component identification/selection.

Figure 3.4 The development cycle compared with the waterfall model.

In a component-based approach the system detailed design will include *selection of the components* that meet or are close to meet the requirements or specification derived from the requirements. The selection process starts with *searching* for the components that are candidate for the selection. Alternatively a new component can be created. In a component-based development process this procedure is less attractive as it requires more efforts and lead-time. However, the components that include core-functionality of the product are likely to be developed internally as they should provide the competitive advantage of the product. The component development goal is not only to produce the component for the particular application, but also for the future applications. The next step in the selection process is component *adaptation*. Thos step may be required if the selected component can be *composed* with other (*instantiated*) components and in a particular phase of the system development *deployed* into the system. The system maintenance and evolution is based on the component *replacement*.

There are many other aspects of component-based development which require specific methods, technologies and management. For example, development environment tools [CL02, PO01], testing, software metrics, legal issues, project management, development process, standardization and certification issues, etc.

#### **Requirements Analysis and Definition**

The analysis activity involves identifying and describing the requirements to be satisfied by the system. Using a component-based approach, an analysis will also include specifications of the

components which are to collaborate to provide the system functionality. To be able to do this, the domain or system architecture which will permit component collaboration must be defined. In component-based development, the analysis include capturing of the system requirements and the definition of the system boundaries, the definition of the system architecture and definition of component requirements to permit the selection or development of the required components. In many cases, for example in product-line architectures, the architecture is a constant that remains unchanged, while components are evolved. In this way the process of development process is simplified as it is reduced on building or selecting new components. On the other hand the initial efforts when a new architecture is being developed may be considerably large, even to that extend that the enterprise developing it cannot afford it.

However a pure top-down approach is an optimistic and an idealized view of the process. It assumes that the component requirements can be precisely defined and that it is possible to find components which satisfy these requirements. In reality we meet several problems [Wal01]; the process of finding components to meet requirements may be very difficult. We can be almost certain that we will not find any component which exactly satisfies the requirements. The next problem that we will meet is the problem of incompatibility of selected component; even if we find components which meet the component requirements defined, it is not at all certain that they will interact as intended when assembled. Very often, when beginning from specific requirements, it is found that there is no component which meets the requirements and the only way to continue the system development is to develop a new component. In reality the process of design and even requirements engineering will be combined with component selection and the evaluation process. Experiences from COTS-based development projects at NASA show that COTS selected drives the requirements to at least some extent [MO00]. In some cases new functionality was discovered in COTS that was useful although not originally planned.

#### **Component Selection and Evaluation**

To perform a search for suitable components and make their identification possible, the components must be specified, preferably in a standardized manner. Again, this may often not be the case. The component specifications will include precisely defined functional interfaces, while other attributes will be specified informally and imprecisely (no method is developed for this) if specified at all. The components selected must therefore be evaluated. The process of evaluation will include several of both technical and non-technical nature. Technical aspects of evaluation include integration, validation and verification. Examples of non-technical issues include the marketing position of the component supplier, maintenance support provided, alternative solutions, etc.

An important method that decreases the risk of selecting a "wrong" component is to identify several component candidates, investigate these, reject those not compliant with the main requirements, continue with the evaluation of the reduced number of candidate components, if necessary refine the requirements, and repeat the evaluation process. This process is known as procurement-oriented requirements engineering [HE01].

In many cases, it may be more relevant to evaluate a set of components composed as an assembly than to evaluate a component. The availability of assemblies is more common than might be expected. Some assemblies may be purchased as functional packages which disintegrate into several components when deployed. Another example of such an assembly is a set of components which, only integrated together, constitutes a functional unit. In such cases, it is necessary to evaluate the assembly; evaluation of the individual components is not sufficient. This implies that an investigation of the integration procedure may be a part of an evaluation. If a component is selected which only partly fulfils the specification on which the selection is based, there are two immediate alternatives: either the component is adapted to the particular specification, or the specification is adapted to the component. A third possibility is the development of a new component. From the system development point of view, this is a bad choice, if this activity were not planned at the beginning of the development process. The consequence of such a decision would require additional resources and development time.

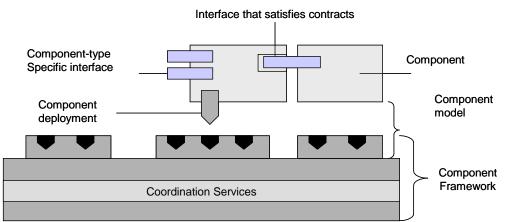

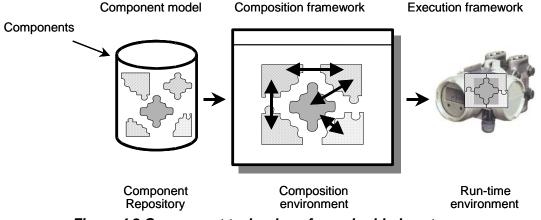

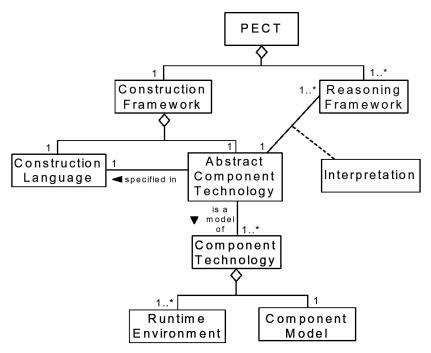

### System Design

In traditional development, the design of the system architecture is the result of the system requirements, and the design process continues with a set of sequences of refinements (for example iterations) from the initial assumptions to the final design goal. In contrast with traditional development, many decisions related to the system design will be a consequence of the component model selected. The initial architecture will be a result of both the overall requirements and the choice of component model. The component model defines the collaboration between the components and provides the infrastructure supporting this collaboration. The more service is provided by the component framework, i.e. by particular component model, the less effort on component and hence system development will be required. Thus, the choice of component model is very important. While many domains will use standard and de-facto standard component models, within particular domains with specific requirements, the specific component models providing particular services will be used, and even internally developed. This is especially true for different embedded systems domains. The design activity is very much determined by the component selection procedure. This procedure begins with the selection of component candidates and continues with consideration of the feasibility of different combinations of these. Consequently the design activity will not be a sequence of refinements of the starting assumptions, but will require a more dynamic and exploratory, and consequently evolutionary approach: The goal will be to find the most appropriate and feasible combination of the component candidates. In this way the results of the design activity may be less predictable, but on the other hand, components will automatically introduce many solutions on the design detail level [PR00,MC00,Le97].

#### **System Integration**

In an ideal component-based development the implementation by coding will be reduced to the creation of the "glue-code" and to component adaptation. Note that if the components selected are not appropriate or an inappropriate model is used, or if the components were not well understood, the costs of glue-code and component adaptation may be larger than that of the development of the components themselves! The effort for the development of glue-code is usually less than 50% of the total development effort, but effort per line of glue-code is about three times the effort per line of the application's code [Ba01]. It should be also noted that it may still be necessary to design and implement some components – those that are business-critical or unique to a specific solution and that some components will require refinement to fit into a given solution.

Integration is the composition of the implemented and selected components to constitute the software system. The integration process should not require great resources, as it is based on the system architecture and the use of deployment standards defined by the component framework and by the communication standard for component collaboration. This is however valid only for syntactic and partially semantic integration. There are several other aspects to be taken into consideration. These are component adaptation, reconfigurations of assemblies and controlling of emerging properties of assemblies integrated into the system.

• *Component adaptation.* In many cases a component must be adjusted to system requirements or to the particular architecture of the system. This adjustment can be achieved in different

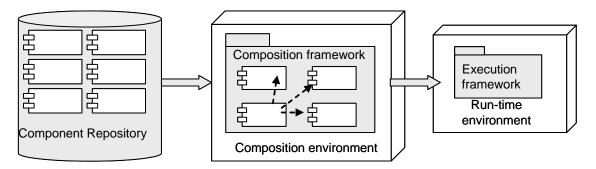

ways – for example by defining component's parameters, or by building a wrapper which will manage the component's inputs and outputs must be developed, and in some cases even a new component that will control particular components and will guarantee the fulfillment of the system requirements.