Mälardalen University Doctoral Thesis No.61

# Efficient Memory Utilization in Resource Constrained Real-Time Systems

Kaj Hänninen

June 2008

School of Innovation, Design and Engineering Mälardalen University Västerås, Sweden

Copyright © Kaj Hänninen, 2008 ISSN 1651-4238 ISBN 978-91-85485-85-7 Printed by Arkitektkopia, Västerås, Sweden Distribution: Mälardalen University Press

# Abstract

This thesis presents design and run-time techniques for efficient memory utilization in embedded real-time systems. The proposed techniques give developers means to reduce the memory consumption in the systems. Altogether, this gives possibilities to increases the added value of industrial systems, in the sense that more features can be fitted on existing hardware.

The thesis begins by presenting the results of a series of interviews concerning common requirements in development of embedded real-time systems. Based on these results, the thesis presents a novel component model for development of resource constrained real-time systems. The model supports efficient memory usage through stack sharing and is formal enough to enable predictability of the resulting stack usage. To provide run-time support for stack sharing, the thesis presents an integration of the stack sharing strategy in an operating system for the component model. To determine the resulting memory usage under stack sharing, a novel analysis method is presented. In an evaluation, the thesis show that the analysis method is both fast and that it gives tight bounds on the resulting stack usage, which makes it suitable for industrial use. The thesis ends with a presentation showing the integration of the proposed analysis technique in an integrated development environment.

The proposed techniques have been integrated in the commercial tool Rubus-ICE from Arcticus Systems. The techniques will be available for developers in the upcoming release of Rubus-ICE.

To Stissen, Chibi, Krutte, Morris and Azze

# Acknowledgements

I wish to thank all my colleagues at Arcticus Systems and Mälardalen Real-Time Research Centre. A special thank you goes out to: Mikael Nolin, Jukka Mäki-Turja, Christer Norström, Markus Bohlin, Jan Carlson, Sasikumar Punnekkat, Kurt-Lennart Lundbäck, John Lundbäck, Hjördis Lundbäck, Mats Lindberg and Staffan Sandberg.

This research has been supported by Arcticus Systems AB<sup>1</sup>, Mälardalen Real-Time Research Centre<sup>2</sup> and SAVE-IT<sup>3</sup>. SAVE-IT is an industrial graduate school supported by the KK-foundation<sup>4</sup>.

Thank you!

Kaj Hänninen

<sup>&</sup>lt;sup>1</sup>www.arcticus-systems.com <sup>2</sup>www.mrtc.mdh.se <sup>3</sup>www.mrtc.mdh.se/projects/save-it <sup>4</sup>www.kks.se

# **List of Publications**

#### Publications included in this thesis

**Paper A:** Kaj Hänninen, Jukka Mäki-Turja, Mikael Nolin, *Present and Future Requirements in Developing Industrial Embedded Real-Time Systems - Interviews with Designers in the Vehicle Domain*, In Proceedings of the 13th Annual IEEE International Conference and Workshop on the Engineering of Computer Based Systems, Potsdam, Germany, March, 2006.

**Paper B:** Jukka Mäki-Turja, Kaj Hänninen, Mikael Nolin, *Efficient Development of Real-Time Systems Using Hybrid Scheduling*, In Proceedings of the 2005 International Conference on Embedded Systems and Applications, Las Vegas, USA, June, 2005.

**Paper C:** Kaj Hänninen, Jukka Mäki-Turja, Mikael Nolin, Mats Lindberg, John Lundbäck, Kurt-Lennart Lundbäck, *The Rubus Component Model for Resource Constrained Real-Time Systems*, To appear in the Proceedings of the 3rd IEEE International Symposium on Industrial Embedded Systems, Montpellier, France, June, 2008.

**Paper D:** Kaj Hänninen, John Lundbäck, Kurt-Lennart Lundbäck, Jukka Mäki-Turja, Mikael Nolin, *Efficient Event-Triggered Tasks in an RTOS*, In Proceedings of the 2005 International Conference on Embedded Systems and Applications, Las Vegas, USA, June, 2005.

**Paper E:** Kaj Hänninen, Jukka Mäki-Turja, Markus Bohlin, Jan Carlson, Mikael Nolin, *Determining Maximum Stack Usage in Preemptive Shared Stack Systems*, In Proceedings of the 27th IEEE Real-Time Systems Symposium, Rio de Janeiro, Brazil, December, 2006. **Paper F:** Kaj Hänninen, Jukka Mäki-Turja, Staffan Sandberg, John Lundbäck, Mats Lindberg, Mikael Nolin, Kurt-Lennart Lundbäck, *Introducing a Plug-In Framework for Real-Time Analysis in Rubus-ICE*, MRTC report ISSN 1404-3041 ISRN MDH-MRTC-229/2008-1-SE, Mälardalen Real-Time Research Centre, Mälardalen University, April, 2008. Submitted to the 13th IEEE International Conference on Emerging Technologies and Factory Automation.

#### Publications relevant to thesis but not included

- Markus Bohlin, Kaj Hänninen, Jukka Mäki-Turja, Jan Carlson, Mikael Nolin, *Bounding Shared-Stack Usage in Systems with Offsets and Precedences*, To appear in the Proceedings of the 20th Euromicro Conference on Real-Time Systems, Prague, Czech Republic, July, 2008.

- Mikael Nolin, Jukka Mäki-Turja, Kaj Hänninen, Achieving Industrial Strength Timing Predictions of Embedded System Behavior, To appear in the Proceedings of the 2008 International Conference on Embedded Systems and Applications, Las Vegas, USA, July, 2008.

- Jukka Mäki-Turja, Mikael Nolin, Kaj Hänninen, Towards Efficient Development of Embedded Real-Time Systems, the Component Based Approach, In Proceedings of the 2006 International Conference on Embedded Systems and Applications, Las Vegas, USA, June, 2006.

#### Other publications by the author

- Kaj Hänninen, Jukka Mäki-Turja, Mikael Nolin, Mats Lindberg, John Lundbäck, Kurt-Lennart Lundbäck, Supporting Engineering Requirements in the Rubus Component Model, MRTC report ISSN 1404-3041 ISRN MDH-MRTC-223/2008-1-SE, Mälardalen Real-Time Research Centre, Mälardalen University, February, 2008.

- Markus Bohlin, Kaj Hänninen, Jukka Mäki-Turja, Jan Carlson, Mikael Nolin, Safe Shared Stack Bounds in Systems with Offsets and Precedences, MRTC report ISSN 1404-3041 ISRN MDH-MRTC-221/2008-1-SE, Mälardalen Real-Time Research Centre, Mälardalen University, January, 2008.

- Markus Bohlin, Kaj Hänninen, Jukka Mäki-Turja, Shared Stack Analysis in Transaction-Based Systems, Work in Progress Proceedings RTSS'07, Tucson, Arizona, USA, December, 2007.

- Kaj Hänninen, Jukka Mäki-Turja, Markus Bohlin, Jan Carlson, Mikael Nolin, *Determining Maximum Stack Usage in Preemptive Shared Stack Systems*, In Proceedings of the 9th Real-Time in Sweden, Västerås, Sweden, August, 2007.

- Jukka Mäki-Turja, Kaj Hänninen, Mikael Nolin, *Efficient Development* of *Real-Time Systems Using Hybrid Scheduling*, In Proceedings of the 9th Real-Time in Sweden, Västerås, Sweden, August, 2007.

- Kaj Hänninen, *Introducing a Memory Efficient Execution Model in a Tool-Suite for Real-Time Systems*, Licentiate Thesis, Mälardalen Real-Time Research Centre, Mälardalen University, September, 2006.

- Kaj Hänninen, Jukka Mäki-Turja, Markus Bohlin, Jan Carlson, Mikael Nolin, Analysing Stack Usage in Preemptive Shared Stack Systems, MRTC report ISSN 1404-3041 ISRN MDH-MRTC-202/2006-1-SE, Mälardalen Real-Time Research Centre, Mälardalen University, July, 2006.

- Kaj Hänninen, Jukka Mäki-Turja, Mikael Nolin, Investigation of Industrial Requirements in Development of Embedded Real-Time Systems, MRTC report ISSN 1404-3041 ISRN MDH-MRTC-185/2005-1-SE, Mälardalen Real-Time Research Centre, Mälardalen University, August, 2005.

- Kaj Hänninen, Jukka Mäki-Turja, Mikael Nolin, *Industrial Requirements in Development of Embedded Real-Time Systems -Interviews with Senior Designers*, In Proceedings of the Work-in-Progress Session of the 17th Euromicro Conference on Real-Time Systems, Palma de Mallorca, Spain, July, 2005.

- Kaj Hänninen, John Lundbäck, Kurt-Lennart Lundbäck, Jukka Mäki-Turja, Mikael Nolin, Introducing Resource Efficient Event-Triggered Tasks in an RTOS, MRTC report ISSN 1404-3041 ISRN MDH-MRTC-170/2005-1-SE, Mälardalen Real-Time Research Centre, Mälardalen University, February, 2005.

- Jukka Mäki-Turja, Kaj Hänninen, Mikael Nolin, *Response Times* in Hybrid Scheduled Systems, MRTC report ISSN 1404-3041 ISRN MDH-MRTC-169/2005-1-SE, Mälardalen Real-Time Research Centre, Mälardalen University, February, 2005.

- Kaj Hänninen, Jukka Mäki-Turja, *Component technology in Re*source Constrained Embedded Real-Time Systems, Technical Report, Mälardalen Real-Time Research Centre, Mälardalen University, March, 2004.

- Toni Riutta, Kaj Hänninen, *Optimal Design*, Master's thesis, Mälardalen University, Department of Computer Science and Engineering, February, 2003.

# Contents

| Ι | Thesis                                              | 1  |

|---|-----------------------------------------------------|----|

| 1 | Introduction                                        | 3  |

|   | 1.1 Thesis problem formulation                      | 5  |

|   | 1.2 Outline of thesis                               | 6  |

| 2 | Real-time systems                                   | 7  |

|   | 2.1 Computational resources                         | 8  |

|   | 2.2 Trends on functionality                         | 8  |

|   | 2.3 Development                                     | 9  |

|   | 2.3.1 Component based development                   | 9  |

|   | 2.4 Execution models                                | 10 |

|   | 2.5 Predicting run-time behaviour                   | 10 |

|   | 2.6 Research on predictable execution models        | 11 |

|   | 2.7 Summary                                         | 12 |

| 3 | Efficient memory utilization through stack sharing  | 13 |

|   | 3.1 Principle of stack sharing                      | 13 |

|   | 3.2 Stack sharing in development                    | 15 |

|   | 3.3 Analysing shared stack usage                    | 16 |

|   | 3.4 Supporting shared stack analysis in development | 19 |

| 4 | Thesis contribution                                 | 21 |

|   | 4.1 Summary of contributions                        | 21 |

|   | 4.1.1 Contributions of included papers              | 22 |

|   | 4.2 Impact of contributions                         | 25 |

| 5 | Conclusion and future work                          | 27 |

| Bibliography |  |

|--------------|--|

|--------------|--|

#### II Included Papers

|   |                                                |                                                                                                        | d Future Requirements in Developing Industrial Em- |                                                                 |  |  |  |  |  |

|---|------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|--|

|   |                                                | bedded Real-Time Systems - Interviews with Designers in the Vehicle Domain                             |                                                    |                                                                 |  |  |  |  |  |

|   | - m                                            |                                                                                                        |                                                    | <b>37</b><br>39                                                 |  |  |  |  |  |

|   | 6.2                                            |                                                                                                        | igation setup                                      | 40                                                              |  |  |  |  |  |

|   | 6.3                                            |                                                                                                        |                                                    |                                                                 |  |  |  |  |  |

|   | 0.5                                            | 6.3.1                                                                                                  |                                                    | 42<br>42                                                        |  |  |  |  |  |

|   |                                                | 6.3.2                                                                                                  | Functional application properties                  | 44                                                              |  |  |  |  |  |

|   |                                                | 6.3.3                                                                                                  | Temporal application properties                    | 45                                                              |  |  |  |  |  |

|   |                                                | 6.3.4                                                                                                  | Operating systems                                  | 46                                                              |  |  |  |  |  |

|   |                                                | 6.3.5                                                                                                  | Execution models                                   | 40                                                              |  |  |  |  |  |

|   |                                                | 6.3.6                                                                                                  | Resource limitations                               | 47                                                              |  |  |  |  |  |

|   |                                                | 6.3.7                                                                                                  |                                                    | 47                                                              |  |  |  |  |  |

|   |                                                | 6.3.8                                                                                                  | Desired tool support                               | 40<br>49                                                        |  |  |  |  |  |

|   | 6.4                                            |                                                                                                        | Software components                                | 49<br>49                                                        |  |  |  |  |  |

|   | 6.4 Discussion - our observations              |                                                                                                        |                                                    |                                                                 |  |  |  |  |  |

|   | 6.5                                            |                                                                                                        | usions                                             | 52                                                              |  |  |  |  |  |

|   | 6.6                                            |                                                                                                        | cation of the investigation results                | 53                                                              |  |  |  |  |  |

|   | Bibl                                           | iograph                                                                                                | у                                                  | 53                                                              |  |  |  |  |  |

| 7 | Don                                            | or B.                                                                                                  |                                                    |                                                                 |  |  |  |  |  |

| 7 | -                                              | Paper B:<br>Efficient Development of Real Time Systems Using Hybrid                                    |                                                    |                                                                 |  |  |  |  |  |

|   |                                                |                                                                                                        | Jevelonment of Real-Time Systems Using Hybrid      |                                                                 |  |  |  |  |  |

|   |                                                |                                                                                                        | Development of Real-Time Systems Using Hybrid      |                                                                 |  |  |  |  |  |

|   | Sch                                            | eduling                                                                                                |                                                    | 57                                                              |  |  |  |  |  |

|   | <b>Sch</b><br>7.1                              | eduling<br>Introd                                                                                      | uction                                             | <b>57</b><br>59                                                 |  |  |  |  |  |

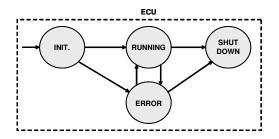

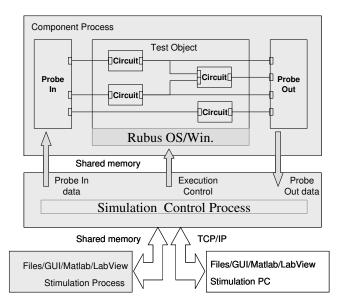

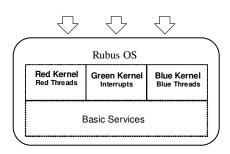

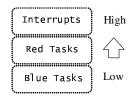

|   | Sch                                            | eduling<br>Introd<br>Syster                                                                            | uction                                             | <b>57</b><br>59<br>61                                           |  |  |  |  |  |

|   | Scho<br>7.1<br>7.2                             | eduling<br>Introd<br>Systen<br>7.2.1                                                                   | uction                                             | <b>57</b><br>59<br>61<br>62                                     |  |  |  |  |  |

|   | <b>Sch</b><br>7.1                              | eduling<br>Introd<br>Syster<br>7.2.1<br>Model                                                          | uction                                             | <b>57</b><br>59<br>61<br>62<br>63                               |  |  |  |  |  |

|   | Scho<br>7.1<br>7.2                             | eduling<br>Introd<br>System<br>7.2.1<br>Model<br>7.3.1                                                 | uction                                             | <b>57</b><br>59<br>61<br>62<br>63<br>64                         |  |  |  |  |  |

|   | Scho<br>7.1<br>7.2<br>7.3                      | eduling<br>Introd<br>System<br>7.2.1<br>Model<br>7.3.1<br>7.3.2                                        | uction                                             | <b>57</b><br>59<br>61<br>62<br>63<br>64<br>65                   |  |  |  |  |  |

|   | Scho<br>7.1<br>7.2<br>7.3<br>7.4               | eduling<br>Introd<br>Systen<br>7.2.1<br>Model<br>7.3.1<br>7.3.2<br>Relate                              | uction                                             | <b>57</b><br>59<br>61<br>62<br>63<br>64<br>65<br>66             |  |  |  |  |  |

|   | Scho<br>7.1<br>7.2<br>7.3                      | eduling<br>Introd<br>System<br>7.2.1<br>Model<br>7.3.1<br>7.3.2<br>Relate<br>Case s                    | uction                                             | <b>57</b><br>59<br>61<br>62<br>63<br>64<br>65<br>66<br>67       |  |  |  |  |  |

|   | Scho<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5        | eduling<br>Introd<br>System<br>7.2.1<br>Model<br>7.3.1<br>7.3.2<br>Relate<br>Case s<br>7.5.1           | uction                                             | <b>57</b><br>59<br>61<br>62<br>63<br>64<br>65<br>66<br>67<br>67 |  |  |  |  |  |

|   | Scho<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6 | eduling<br>Introd<br>System<br>7.2.1<br>Model<br>7.3.1<br>7.3.2<br>Relate<br>Case s<br>7.5.1<br>Conclu | uction                                             | <b>57</b><br>59<br>61<br>62<br>63<br>64<br>65<br>66<br>67       |  |  |  |  |  |

29

35

| 8  |            | er C:<br>Rubus Component Model for Resource Constrained Real-<br>e Systems | 75       |

|----|------------|----------------------------------------------------------------------------|----------|

|    | 8.1        | Introduction                                                               | 77       |

|    | 8.2        | Engineering requirements on RubusCMv3                                      | 78       |

|    | 8.2<br>8.3 | Objective of RubusCMv3                                                     | 79       |

|    | 8.4        |                                                                            | 80       |

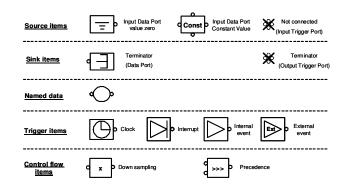

|    | 8.4        | The RubusCMv3 component model                                              | 80<br>80 |

|    |            | 8.4.1 Software logic                                                       | 80<br>84 |

|    | 05         | 8.4.2 Real-time properties in RubusCMv3                                    | -        |

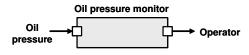

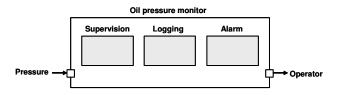

|    | 8.5        | System example                                                             | 85       |

|    | 8.6        | System development using RubusCMv3                                         | 89       |

|    | 8.7        | Conclusions and future work                                                | 91       |

|    | Bibli      | ography                                                                    | 92       |

| 9  | Pape       | er D:                                                                      |          |

|    | Effic      | ient Event-Triggered Tasks in an RTOS                                      | 97       |

|    | 9.1        | Introduction                                                               | 99       |

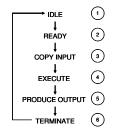

|    | 9.2        | The single shot execution model (SSX)                                      | 99       |

|    | 9.3        |                                                                            | 01       |

|    | 9.4        | 1 01                                                                       | 03       |

|    | 9.5        | e                                                                          | 05       |

|    |            |                                                                            | 05       |

|    |            |                                                                            | 06       |

|    |            | 11 1                                                                       | 109      |

|    | 9.6        |                                                                            | 109      |

|    |            |                                                                            | 10       |

|    | DIUII      |                                                                            | .10      |

| 10 | Pape       |                                                                            |          |

|    |            | rmining Maximum Stack Usage in Preemptive Shared Stack                     |          |

|    | Syste      |                                                                            | 13       |

|    |            |                                                                            | 15       |

|    | 10.2       | Related work                                                               | 16       |

|    |            | 10.2.1 Stack analysis                                                      | 16       |

|    |            | 10.2.2 Preemption analysis                                                 | 17       |

|    | 10.3       | Stack analysis of preemptive systems                                       | 17       |

|    |            |                                                                            | 20       |

|    |            |                                                                            | 20       |

|    | 10.5       |                                                                            | 21       |

|    |            |                                                                            | 24       |

|    | 10.5.2 Computational complexity                           | 124 |

|----|-----------------------------------------------------------|-----|

|    | 10.6 Evaluation                                           | 125 |

|    | 10.6.1 Simulation setup                                   | 126 |

|    | 10.6.2 Results                                            | 127 |

|    | 10.7 Conclusions and future work                          | 129 |

|    | Bibliography                                              | 131 |

|    |                                                           |     |

| 11 | Paper F:                                                  |     |

|    | Introducing a Plug-In Framework for Real-Time Analysis in | I   |

|    | Rubus-ICE                                                 | 137 |

|    | 11.1 Introduction                                         | 139 |

|    | 11.2 Rubus                                                | 140 |

|    | 11.2.1 Rubus-ICE                                          | 140 |

|    | 11.3 Plug-in framework for Rubus-ICE                      | 141 |

|    | 11.3.1 Requirements on the plug-in framework              | 141 |

|    | 11.3.2 Requirements on Rubus-ICE plug-ins                 | 143 |

|    |                                                           | 143 |

|    |                                                           | 144 |

|    |                                                           | 147 |

|    |                                                           | 148 |

|    | -                                                         | 150 |

|    |                                                           | 151 |

|    |                                                           |     |

Ι

# Thesis

## **Chapter 1**

# Introduction

Embedded computers play an important role in people's everyday life. Products that used to be purely mechanical have incorporated computers to control features and provide possibilities for more advanced functionality. Nowadays, we can find computers in washing machines, DVD players, cellular phones, cars and in a multitude of other products.

Throughout the years, the number of embedded systems has been increasing and the trend indicates that the number of embedded systems will continue to increase. With every new release of a system, the number of advanced features is increasing either due to customer demands, legislation requirements or simply because manufacturers want to increase the added value of their products by incorporating new features. As a consequence, the complexity in development of embedded systems is increasing.

Component based development is slowly gaining popularity as a development discipline in the embedded domain. The component based development discipline enables system development at different levels of abstraction through hierarchical composition of software units, i.e., components. It has been successfully used in development of complex desktop applications for quite some time, and is now being introduced as an alternative, and promising, way to cope with the complexity in development of embedded systems.

Even though component based development has been introduced for embedded development, many embedded systems are still being realized with considerably simple methods. These methods originates from way back when embedded systems almost exclusively consisted of control features, i.e., systems in which all features have similar, typical hard real-time, requirements. Today however, the diversity of features, and mixture of real-time requirements in embedded systems, entail that these development methods are adequate only for a subset of the features in a system. For instance, in real-time systems, static scheduling is often used and sometimes even mandated, for realization of safety critical functionality. For reasons, such as, tradition in development, simplicity of use, or lack of proper support in development tools, static scheduling is sometimes used to realize all features. Even though researchers have proposed a large number of alternative models, in practice however, only a few of the proposed models are used and supported in industrial development tools. This implies that developers often force fit functionality with different requirements to be executed under a single execution model, such as the static scheduled model. This force fitting of functionality increases software complexity and leads to poor resource utilization.

Many embedded systems are resource constrained in the sense that they have a limited amount of computational resources. Processors for embedded systems have only a fraction of the processing power of desktop computers. In addition, the amount of available memory in embedded systems is significantly lower than what is common in desktop computers. To improve resource utilization, additional execution models need to be introduced in development. However, not all execution models are suitable for embedded systems. In fact, an execution model must be introduced with care, since different sub-domains within the embedded domain have different requirements that need to be supported by the execution model. Properties such as safety and reliability are considered important and need to be addressed in development of embedded systems. This implies that execution models need to be verifiable, e.g., by formal analysis or manual testing. This in turn, require analysis methods applicable for industrial use, i.e., analysis methods that are easy to use and have low timing complexity.

This thesis will show how software development for embedded real-time systems can be made more efficient, with respect to hardware utilization. Specifically, the thesis will present the integration of a predictable memory efficient execution model, denoted stack sharing, in a development context for component based development of embedded real-time systems. To address the issues outlined in the introduction, the thesis presents a novel component model that support common requirements in development of control systems for ground vehicles. The component model supports multiple execution models, giving developers means to avoid force fitting of functionality. Also, the component model is developed to support predictable and efficient memory usage through stack sharing. To achieve efficient memory usage at run-time, the

thesis presents an integration of stack sharing in an operating system for the proposed component model. In addition, a novel analysis method to predict the memory consumption under stack sharing is presented and integrated in a development environment.

#### 1.1 Thesis problem formulation

To facilitate efficient development of complex industrial embedded systems, suitable development models and efficient execution models for realization of the systems are needed. The models should facilitate development of resource constrained systems and allow features with different real-time requirements to be realized in a single system. Also, the models need to be formal enough for analysis and verification of properties and requirements. At the same time, to gain industrial use, the models need to be adapted to the specific requirements in industrial development and integrated in development tools. Addressing these issues, this thesis investigates the following:

- What are the requirements in development, and properties, of embedded real-time systems?

- How can industrial real-time systems benefit from additional execution models?

Based on these investigations, the thesis then address:

- Component based development of embedded real-time systems, supporting efficient memory usage through stack sharing.

- Integration of stack sharing in a run-time environment.

- Predictability of the memory consumption under stack sharing, through formal analysis methods.

- Integration of an analysis method for stack sharing, in a development environment.

#### **1.2** Outline of thesis

The reminder of this thesis is outlined as follows:

#### Part I

**Chapter 2** presents the background for the work conducted in this thesis. The chapter gives an introduction to real-time systems, development of real-time systems and execution models for real-time systems.

**Chapter 3** presents an efficient execution model, called stack sharing, for real-time systems. The chapter outlines issues that need to be considered in integration of stack sharing in a commercial development environment. The chapter also presents how this thesis addresses these issues in integrating the model in a development context.

**Chapter 4** presents the overall contribution of the thesis. The chapter also outlines the contribution of the author.

**Chapter 5** concludes the work presented in this thesis and presents directions for future work.

#### Part II

Part II of this thesis contains six papers that constitute the scientific contributions of this thesis.

## Chapter 2

## **Real-time systems**

Real-time systems can be found almost everywhere today. Many of us use them on a daily basis. For example, a modern car contains some 40-80 computers, most of which are classified as real-time systems. Most real-time systems are embedded systems that interact with the environment by sensors and actuators. An embedded real-time system in a car, for example, can be responsible of controlling functions such as anti-lock braking, anti-skid, traction control and other safety features as well as entertainment features.

The main distinction between real-time systems and conventional desktop systems stem from the way in which timing is considered. In conventional computer systems such as desktop systems, functional correctness is of main concern, whereas real-time systems emphasize both functional and timing requirements in computing.

The air bag, a safety feature in most cars, is a classical example that demonstrates timing requirements in a computer system. The air bag is an inflatable nylon bag, activated at collision and filled with a gas to protect the passengers. There are several timing aspects that need to be considered for correct functionality of an air bag. Inflating the bag too early, i.e., directly when the collision is detected, might render the bag useless, in the sense that the gas may already have escaped the bag when the passenger hits the bag. Inflating the bag too late, might actually be dangerous for passengers, in the sense that the inflating bag may hit the person with a great force. In essence, to provide proper protection, the bag needs to be inflated within a certain time interval after the collision is detected. The air bag is a typical feature with strict timing requirements and thus can be classified as a real-time system.

#### 2.1 Computational resources

Most embedded real time systems are resource constrained in some sense. The processing power and the amount of memory in the systems are usually only a fraction of what is common in desktop computers. For instance, back in 1990, a processor running at 25MHz was considered as high performance in a desktop system. Nowadays, with processor speeds reaching 4GHz, processors running at 25MHz are of no use in desktop computers. However, in the embedded domain, the use of low performance processor, such as 25MHz processors, is not unusual. In addition, the amount of memory in a typical embedded system is not even comparable to what is common in desktop computers. Typically, the amount of available memory in embedded systems lies in the range of kilobytes to mega-bytes. It is not uncommon that the features of a real-time system are realized by, as many as, hundreds of threads that execute and compete for the available resources in the same system. Hence, the limited resources in embedded systems need to be utilized in an efficient way.

#### 2.2 Trends on functionality

Products that used to be purely mechanical have incorporated computers to provide more advanced features and to increase the added value of the products. Incorporating computers in products offers flexibility in the sense that new features can be added in the computer software. The software in modern embedded real-time systems account for an important part of the value growth of the products [HNN08]. Embedded real-time systems have, by tradition, been used to control physical processes. Consequently, the software in these systems consisted almost exclusively of control algorithms with strict timing requirements. With the flexibility offered by software, the number of features introduced in embedded real-time systems has been increasing over the years. Nowadays, embedded real-time systems are often responsible for handling a variety of different type of features with different requirements. For instance, a typical embedded real-time system in a passenger car manages control features, driving assistance, information and entertainment features [SVN07]. This implies that embedded real-time systems need to manage both safety critical features as well as less critical features in the same system. In addition, the trend indicates that the number of features in embedded real-time system will continue to increase.

#### 2.3 Development

The fact that many embedded real-time systems contain a mix of features with requirements ranging from hard real-time to soft, and even non real-time, raises challenges that developers of these systems need to deal with to deliver safe and reliable solutions.

Historically, embedded real-time systems have been developed using low level programming languages to guarantee full control over the system behaviour. Throughout the years however, development of embedded real-time systems has undergone changes to support the diverging requirements on applications. High level programming languages (for example C, C++, and Java) have been adopted as alternatives to the traditional low level programming languages. A recent trend is the introduction of component based development in the embedded community.

#### 2.3.1 Component based development

Component based development is a discipline in which software systems are built by assembling pieces of software units known as components. Many component based development methodologies allow hierarchical composition of components, enabling development of systems at variable levels of abstraction. Abstracting away unnecessary details, allowing developers to focus on the problem at suitable abstraction levels, is in many cases a key in developing complex systems. In the office-/Internet-area component based development has had a tremendous impact. It has shown to be successful in development of complex applications and is slowly gaining popularity in the embedded domain. The main problem to adapt component based development to the embedded domain has been the lack of tools and component models that are able to fulfil domain specific requirements on safety and reliability as well as predictable and efficient resource usage for embedded systems. For this reason, many real-time systems are still developed with considerably simple methods, with main focus on guaranteeing functional correctness and temporal properties.

To support efficient component-based development of embedded real-time systems, at least three viewpoints should be taken in consideration, (i) the developers view, (ii) the analysis view, (iii) the view of the run-time system. These viewpoints need to be jointly approached to find a suitable trade-off between the requirements that need to be fulfilled. For example, a developer (or designer) of a system should have a component model, architectural rules and constraints at his disposal to develop a high level (abstract away from pure source code) architecture of the application (system). From the analysis viewpoint, the design/architecture must be formal enough so that automated analysis techniques, such as response time and memory utilization analysis, can be performed. Finally, the run-time system should have a small run-time footprint, but still provide sufficient run-time services to the components of the application.

#### 2.4 Execution models

In development of embedded real-time systems, a developer must choose an execution model to realize functionality. In general, an execution model can be seen as a method that provides ways to execute features, i.e., to carry out the functionality in a computer system. Each execution model affects the utilization of the processor as well as the memory consumption. For developers to utilize an execution model, the execution model needs to be supported at design and run-time, e.g., by a component model and by an operating system. Many operating systems only provide a few (often only one) execution models. In addition, very few component models have been explicitly designed to support multiple execution models. This implies that developers have to force fit functionality with diverging requirements to be executed under a single execution model. Force fitting functionality to be executed under a single execution model often results in increasing software complexity and poor resource utilization. Hence, as the need for new features in products increases, better usage of the limited computational resources is needed. This can be achieved by introducing resource efficient and predictable execution models in development.

#### 2.5 Predicting run-time behaviour

To enable predictability of systems run-time behaviour, developers annotate models of real-time systems with temporal properties and requirements. Temporal requirements are often the ones in focus when predictability of real-time systems is addressed. With the increasing amount of functionality in resource constrained real-time systems, the need to verify properties such as timing and memory consumption, becomes more important.

There are a number of ways to verify timing requirements and to derive bounds on memory consumption in real-time systems. In an industrial context, verification of a system is often performed by executing the system and measuring the properties. To verify whether a system meets its requirements, the measurements are compared with the requirements. It is obvious that such a verification approach seldom gives safe results, i.e., that the requirements are fulfilled, simply because the measurements must represent the worst case behaviour of the properties affecting the verification. Executing a system in a worst case manner with respect to some property, is non trivial and extremely hard to accomplish. Even so, this kind of verification is common in industry. In a more formal context, the requirements on a real-time system can be verified by mathematical analysis methods. Throughout the years, the research community have been active and proposed numerous analysis methods for real-time systems (see for example [ABT+93, BTW95, EHS97, KAS93, Leh90, Pun97, SRL87, SRL90, TB94, TC94, THW94, Tin92]). These methods are however non trivial to understand and often hard to incorporate in an industrial context. Experience shows that analysis methods are not easily transferred from an academic environment to industry [LR03, WAN03]. There are many reasons for this, originating foremost from differences in requirements and assumptions between industry and academia [NMTH08]. In addition, many analysis methods are applicable to small artificial systems, and experience therefore high timing complexity when applied to large real world systems. In essence, to successfully transfer complex analysis methods from academia to industry, the methods need to be incorporated in development tools and adhere to the requirements in the context in which they are integrated.

#### 2.6 Research on predictable execution models

Research on real-time systems has provided a number of different scheduling algorithms, analysis methods and execution models, see, e.g., [ABRW91, But97, Liu00, LL73, SEF98, SSL89, SSRB98, XP90]. Recent results in real-time scheduling theory, e.g., [AB98, Abe98, Bak90, BBLB03, MTN05, PG03], make it possible to combine several execution models in one system (and still achieve predictable timing and efficient resource usage). However, these techniques by themselves, do not remove any problems. In addition, a change in the software development model and tools is needed.

Most of the execution models and analysis techniques proposed by the realtime research community have been developed with timing in focus. The aim of these models has been to guarantee predictability of timing requirements and to improve CPU utilization. Even though it is known that most embedded real-time systems are resource constrained and that the systems need a certain amount of memory to realize features, relatively little work has been done on execution models and analysis for efficient memory utilization. A common problem that need to be addressed, when introducing means for efficient memory utilization in real-time systems, concerns how analysability of temporal requirements of functionality executed under the model can be guaranteed. Hence, models for efficient memory utilization should be predictable with respect to both the memory usage and timing behavior. There exist however, techniques to improve the memory usage in real-time systems, see for example [Bak90, CMM<sup>+</sup>04, CRM06, DMT00, GD07, GLN01, Dig, MSB05, Ros06, RRW05]. One of them is stack sharing.

Stack sharing is an execution strategy that allows several tasks to share a common memory area for execution. It is a strategy suitable for many type of systems in the sense that it reduces the overall memory consumption and puts only a few restriction on system development. For stack sharing to be successful, the strategy in itself needs to be integrated and supported by a development environment. Moreover, analysis methods that are able to give tight bounds on the resulting stack usage, under stack sharing, and that are applicable in an industrial setting, are needed.

#### 2.7 Summary

With the increasing amount of diverging functionality in embedded real-time systems, ranging from safety critical functionality to non critical functionality, suitable and efficient execution models should be supported in development. Stack sharing is such a model. It is a predictable model applicable to a wide range of real-time systems.

To gain acceptance in industry, the model needs to be supported in tools and development models, such as component models. Moreover, to provide possibilities for predictability, analysis methods for stack sharing are needed. These methods should be applicable in an industrial setting, i.e., they should be developed to support relevant system models and give tight results whilst having low timing complexity. The analysis methods then need to be integrated in tools and adapted to the requirements in industrial development.

### **Chapter 3**

# Efficient memory utilization through stack sharing

#### 3.1 Principle of stack sharing

Computer systems utilize threads and processes to realize features. In realtime systems, the sequential execution of program code is usually performed by tasks. Each task requires a certain amount of memory and execution time to realize a feature, i.e., to execute the code that define the feature. A task is commonly defined by (i) a task control block (ii) the actual task code (program code) and (iii) a stack memory area.

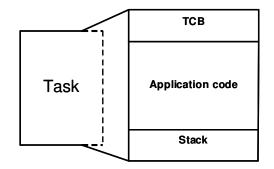

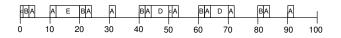

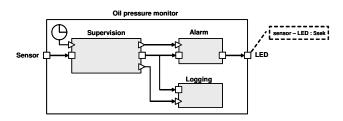

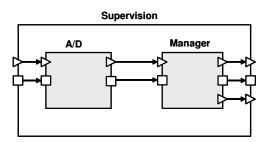

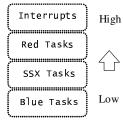

Figure 3.1: Common task structure. Each task has its own stack

#### 14 Chapter 3. Efficient memory utilization through stack sharing

The task control block is used to save the internal states of a thread. The task code is the application written by a developer and the stack is a memory area commonly processed in a last-in-first-out manner. The stack is used to store register values, function parameters, local variables and memory addresses. In most computer systems, each task has its own stack area allocated (see Fig. 3.1). Consequently, in systems with a large number of tasks the total amount of memory needed for the run-time stacks can be large. In addition, many systems allow high priority interrupts to utilize the stack of a task, implying that each task also need to have stack space allocated for interrupts.

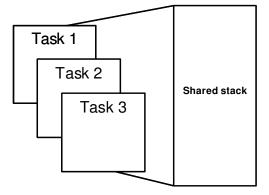

To reduce the amount of stack memory in systems, stack sharing can be supported among tasks. Stack sharing is an execution strategy that allows several tasks to share a common memory area as a shared run-time stack (Fig. 3.2).

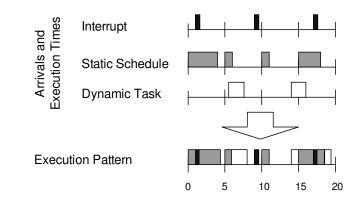

Figure 3.2: Stack sharing among tasks. Several tasks utilize the same stack

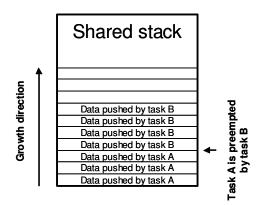

The principle of stack sharing is very simple. It is easiest demonstrated by an example. Consider two tasks (task A and task B) sharing a stack. Say that task A executes and pushes data, i.e., adds data to the stack, and later on gets preempted by task B. Then task B simply continues to utilize the stack from the preemption point (see Fig. 3.3). This implies that the stack pointer, i.e., the pointer to the first available memory area in the stack, needs to be shared among task A and task B. The possibility to reduce the total memory usage under stack sharing, originates from the fact that several tasks can actually share the same memory cells at different points in time. In essence, the basic principle is to save resources by sharing them.

Figure 3.3: Stack sharing between task A and task B. When task A is preempted by task B, task B continues to utilize the stack from the preemption point

Throughout the years, a number of publications, e.g., [Bak90, CMM<sup>+</sup>04, DMT00, GLN01, GD07, MSB05, RRW05] have addressed stack sharing. Stack sharing has been supported by interrupt-driven systems for quite some time and has also been adopted for pure time-driven and hybrid (static and dynamic) scheduled preemptive systems. Stack sharing is currently supported by a number of operating systems, e.g. Rubus RTOS[Arc], Fusion RTOS[Uni], Erika RTOS[Evi], SMX RTOS[Dig].

#### 3.2 Stack sharing in development

Stack sharing is suitable for many types of systems in the sense that it is easy to use and that it introduces only a few, mainly two, restrictions in development. Under stack sharing, tasks are (i) prohibited to self suspend, (e.g., timed sleep or other delay functions may not be used in the application code of task that participate in stack sharing) and (ii) task synchronization, e.g., access to shared resources, should be done using an early blocking resource access protocol such as the Immediate Priority Ceiling Protocol[BW96] or Stack Resource Policy[Bak90]. By adhering to these restrictions, developers can utilize stack sharing for a number of different types of systems, both preemptive and non-

preemptive systems.

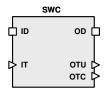

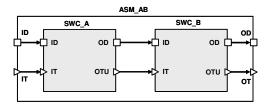

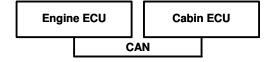

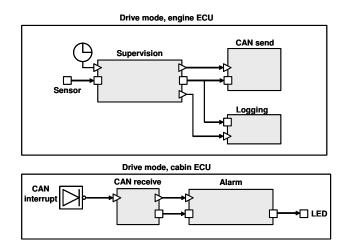

To utilize stack sharing in systems development, tools as well as run-time environments and development methods need to have support for stack sharing. For instance, in a component based development context, stack sharing need to be supported by the component model. This implies that components need to have their run-time semantics specified in such way that they do not violate the above restrictions. Moreover, the component model needs to be formal enough to allow analysis of memory consumption under stack sharing. Paper C in this thesis proposes a novel component model, for resource constrained systems, that support stack sharing. The model enforces a run-to-completion semantics on the software logic to support stack sharing. Furthermore, to enable shared stack analysis, each software item in the model has an execution profile that denotes the individual stack usage of the item. In addition, the run-time environment that provides the execution of the components (often a real-time operating system), also needs to provide support for stack sharing. Introducing support for stack sharing, i.e., an additional execution model, in a real-time operating system, requires careful design to minimize the overhead of the new model and side effects (both temporal and spatial) affecting predictability of the existing models. Paper D, addresses these issues and presents an integration of stack sharing in a real-time operating system with multiple execution models.

#### **3.3** Analysing shared stack usage

When developing systems, with or without stack sharing, the memory that constitutes a stack must be allocated. Hence, a developer needs to calculate or estimate the total amount of memory needed for a stack. This is non-trivial in the sense that the actual stack usage of a task, thus the memory required, depends on many factors, e.g., the number of variables in the application code and the way functions are called from within a task etc. It is imperative that the amount of memory allocated for the stack is enough for a task to realize a feature. Serious errors, such as stack overflow can occur if a task need more stack than it has allocated. Stack errors, such as overflows, are considered extremely hard to detect since overflows are often sporadic.

There are basically two common ways to come up with the total amount of memory required for a stack. In industry, the total amount of memory is often estimated. The stack is then allocated with the estimated size. The system is then simply executed and the stack usage of tasks is monitored. This may be achieved by filling the stack area with pre-determined values before the system is executed. When the system is terminated, the number of values being overwritten in the pre-determined pattern gives an idea of the stack usage under the particular execution scenario. This is, of course, not a fool proof way of determining the amount of memory required for a stack, however, it is not an uncommon method. A more formal way to determine the stack size needed for a task, may be done by tools such as [Tid, Abs].

In stack sharing, additional properties need to be considered in determining the maximum amount of memory required for a shared stack. Determining the worst-case memory usage, i.e., total amount of memory required for the shared stack in preemptive systems, require:

- Analysis of stack usage of individual tasks (or threads)

- · Analysis of possible preemptions among tasks in the system

Hence, under stack sharing, preemption patterns, i.e., the way in which tasks may preempt each other, affects the amount of memory required for the shared stack. A number of publications have addressed shared stack analysis (see for example [DMT00, GLN01, GD07, RRW05, CMM<sup>+</sup>04]).

Performing a preemption analysis, i.e., determining the possible preemption patterns, is more or less complex depending on the system model. For example, under priority based execution, priorities are used to dispatch tasks for execution, i.e., a task with high priority may preempt a task with low priority. Hence, the number of unique priorities in the system defines a maximum preemption depth. A commonly used engineering approach to determine the total shared stack usage in priority-based systems is to estimate the maximum stack usage of individual tasks and then compute the sum of maximum stack usage for each priority level. Thus, it is an approach that always assumes fully nested preemption pattern among tasks, and do not consider the actual preemptions that can occur between tasks. From a preemption point of view, this is a safe approach, but it may in many cases be pessimistic and result in rather poor stack utilization. This can be demonstrated with a simple example. Consider the task set in Table 3.1, where P denotes the priority, T denotes the period time an C the worst case execution time of the tasks.

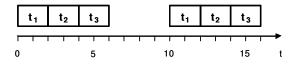

Assume that all tasks in the example share a common stack, and that all tasks are activated at t = 0, then the traditional engineering approach would require the shared stack to be 30 bytes (sum of maximum stack usage in each priority level). However, considering the information we have about the system in the example, it is easy to see that no preemption can occur between the tasks (see trace in Fig. 3.4). Hence 10 bytes would be enough for the shared stack.

| tole 5.1. All example. Task set ill a preemptive system |        |    |   |                     |  |

|---------------------------------------------------------|--------|----|---|---------------------|--|

| Task                                                    | Р      | Т  | С | Stack usage (bytes) |  |

| $	au_1$                                                 | High   | 10 | 2 | 10                  |  |

| $	au_2$                                                 | Medium | 10 | 2 | 10                  |  |

| $	au_3$                                                 | Low    | 10 | 2 | 10                  |  |

Table 3.1: An example: Task set in a preemptive system

Figure 3.4: Execution trace of task set in Table 3.1

Improving shared stack usage can be achieved by changing the task attributes, which may or may not change the system behaviour, or by improving the analysis method, i.e., reducing the pessimism of the method. For example, the priorities of the tasks in the example could be altered without affecting the temporal behaviour or the actual functionality realized by the tasks. The tasks could all have been assigned high priority and still execute exactly as the original system, i.e., an execution trace would look like in Fig. 3.4. The traditional analysis would now yield in a shared stack usage of 10 bytes. Another approach to improve stack analysis is to improve the preemption analysis, i.e., the preemption analysis should reflect only the preemption patterns that actually can occur. This approach differs from the previous one in the sense that it does not require any modifications of priorities or other task attributes.

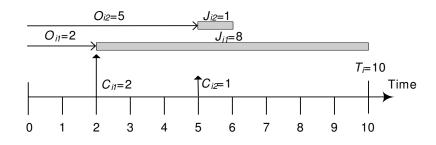

The fact that a task may only be preempted during its execution, need to be considered when improving a preemption analysis. Basically this means that a task can only be preempted in a time interval defined by its actual start time and actual finishing time. Considering this interval as a possible time for preemption, would improve shared stack analysis. However, the actual start time and the actual finishing time of a task are dynamic parameters that may change from one execution to another. In many systems however, these dynamic parameters can be bounded by static compile time properties. These bounds can then be used to improve the preemption analysis. Such an approach is presented in Paper E. The dynamic parameters are bounded by offsets and worse case response times. These bounds reflect the possible time interval in which a task may execute and possibly be preempted. The method presented in paper E, is applicable for industrial systems in the sense that it has reasonably low timing complexity and it is developed for an industrially used system model.

#### **3.4** Supporting shared stack analysis in development

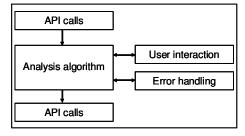

For stack sharing to be accepted in an industrial development context, the analysis method for predictability of the resulting stack usage needs to be supported in development tools, e.g., in an Integrated Development Environment (IDE). As with many analysis methods, stack analysis is complex and hard to implement by non-experts. Hence, means to integrate complex analysis in development environments are needed. The plug-in concept is a promising way to achieve this.

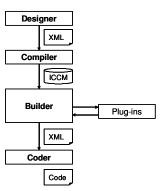

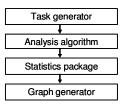

In resent years, plug-in based tools have gained popularity. These tools allow plug-ins to extend the features of the tool. For example, Eclipse [Ecl], an open development platform, allows plug-ins to extend the functionality of the Eclipse platform. Plug-ins can be seen as programs that provide certain functions by interacting with a host application. In essence, plug-ins can be developed in isolation and then integrated with a host application. This makes the concept suitable for integration of complex analysis methods in a development environment. Supporting plug-ins in a development environment allows researchers, the experts on analysis methods, to develop their analysis methods in isolation. These methods can then be plugged-in in a development environment. Paper F in this thesis presents the development of a plug-in framework for integration of real-time analysis methods in Rubus-ICE [Arc]. The paper outlines requirements on the framework as well as the development of application programming interface enabling plug-ins to interact with its host application. Even though a plug-in concept eases the integration of analysis methods in industrial tools, a number of issues still need to be considered for successful integration of analysis methods in an industrial context. For example, the fact that analysis methods are transferred from a controlled research setting to an industrial setting, requires extensive error handling to be introduced in analysis methods. Moreover, even though the implementation of an analysis method may have been verified in a research setting, it often needs to be verified again once integrated. Paper F presents some of the issues that need to be considered from an analysis developer's view.

# **Chapter 4**

# **Thesis contribution**

This thesis presents scientific contributions for development of embedded resource constrained real-time systems. By taking advantage of the novel execution models provided by the research community, the contributions show that efficient memory utilization can achieved in embedded real-time systems.

# 4.1 Summary of contributions

The contributions of this thesis can be summarized as follows. The thesis present:

- A summary of properties and common requirements in development of industrial embedded real-time systems.

- A demonstration of how development of embedded real-time systems can be made more efficient, with respect to hardware utilization, by introduction of additional execution models.

- A component model, supporting efficient and predictable stack usage, for embedded real-time systems.

- An implementation of a memory efficient execution model in a real-time operating system.

- An analysis method, suitable for industrial use, for verification of the memory efficient execution model.

• The integration of analysis methods in an IDE for development of embedded real-time systems.

These contributions are presented in the following scientific papers.

#### 4.1.1 Contributions of included papers

**Paper A:** Kaj Hänninen, Jukka Mäki-Turja, Mikael Nolin, *Present and Future Requirements in Developing Industrial Embedded Real-Time Systems - Interviews with Designers in the Vehicle Domain*, In Proceedings of the 13th Annual IEEE International Conference and Workshop on the Engineering of Computer Based Systems, Potsdam, Germany, March 2006.

Paper A presents common requirements in development of vehicular embedded real-time systems. The requirements were collected in a series of interviews with ten senior designers from four Swedish companies. The paper shows that reliability and safety are the main properties in focus during development. It also shows that the amount of functionality has been increasing in the systems and that requirements are fulfilled using considerably homogenous development methods. The paper also show that there will be even stronger requirements on dependability and control performance and that requirements on soft and resource demanding functionality will continue to increase.

**Personal contribution:** Kaj was the main author of the paper and has been involved in all parts of the work. He was responsible of preparing the study and establishing the research questions. Furthermore, he coordinated the interviews and compiled the results.

**Paper B:** Jukka Mäki-Turja, Kaj Hänninen, Mikael Nolin, *Efficient Development of Real-Time Systems Using Hybrid Scheduling*, In Proceedings of the 2005 International Conference on Embedded Systems and Applications, Las Vegas, USA, June 2005.

Paper B show how developers can benefit from additional execution models in development. An industrial case study demonstrate how multiple execution models enables more efficient use of computational resources, resulting in a cheaper or more competitive product and that more functionality can be fitted into legacy, resource constrained, hardware.

**Personal contribution:** Kaj has been involved in the case study part of the paper. He provided the basis, i.e., system information and requirements for the case study.

**Paper C:** Kaj Hänninen, Jukka Mäki-Turja, Mikael Nolin, Mats Lindberg, John Lundbäck, Kurt-Lennart Lundbäck, *The Rubus Component Model for Resource Constrained Real-Time systems*, To appear in the Proceedings of the 3rd IEEE International Symposium on Industrial Embedded Systems, Montpellier, France, June, 2008.

Paper C presents a component model for development of embedded systems for ground vehicles. The industrial requirements presented in paper A were considered for the component model. The model aims at supporting design, analysis as well as efficient and predictable stack usage.

**Personal contribution:** Kaj was the main author of the paper. He has been involved in all parts of the work.

**Paper D:** Kaj Hänninen, John Lundbäck, Kurt-Lennart Lundbäck, Jukka Mäki-Turja, Mikael Nolin, *Efficient event-Triggered Tasks in an RTOS*, In Proceedings of the 2005 International Conference on Embedded Systems and Applications, Las Vegas, USA, June 2005.

Paper D presents an implementation of a resource efficient execution model in a real-time operating system. The model is suitable for component based control software. The execution model, denoted single-shot execution (SSX), is realized with very simple and resource efficient run-time mechanisms and is highly predictable, hence suitable for use in resource constrained real-time systems. The paper also presents an evaluation, showing that significant memory reductions can be obtained by stack sharing.

**Personal contribution:** Kaj was the main author of the paper and has been involved in all parts of the work. He was responsible of implementing the execution model in the operating system and evaluating the implementation.

**Paper E:** Kaj Hänninen, Jukka Mäki-Turja, Markus Bohlin, Jan Carlson, Mikael Nolin, *Determining Maximum Stack Usage in Preemptive Shared Stack Systems*, In Proceedings of the 27th IEEE Real-Time Systems Symposium, Rio de Janeiro, Brazil, December, 2006.

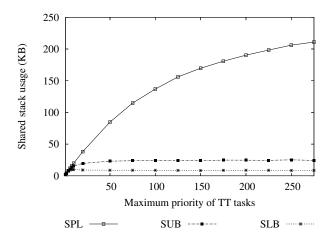

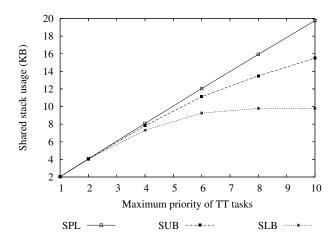

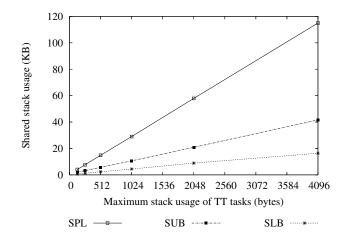

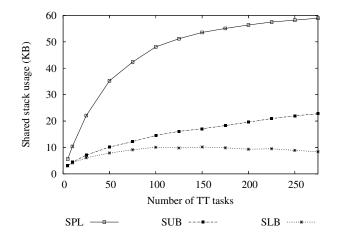

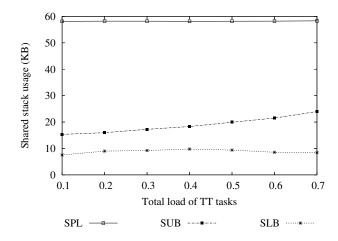

Paper E presents methods to determine the maximum stack memory used in preemptive, shared stack, real-time systems. A general and exact problem formulation applicable for any preemptive system model is presented. The exact formulation is however, not suitable for development of industrial systems, because it based on dynamic properties. The paper also presents an approximate analysis method that is suitable for industrial use. The method safely approximate the total stack usage by using static (compile time) information about the system model and the underlying run-time system. The approximate method supports a relevant and commercially available system model: A hybrid, statically and dynamically, scheduled system. Evaluations show that the approximate method significantly reduces the amount of stack memory needed, when compared to a traditional analysis technique.

**Personal contribution:** Kaj was the main author of the paper. He initiated and coordinated the work and did the background research. He was also responsible for parts of the implementation and did the evaluations.

**Paper F:** Kaj Hänninen, Jukka Mäki-Turja, Staffan Sandberg, John Lundbäck, Mats Lindberg, Mikael Nolin, Kurt-Lennart Lundbäck, *Introducing a Plug-In Framework for Real-Time Analysis in Rubus-ICE*, MRTC report ISSN 1404-3041 ISRN MDH-MRTC-229/2008-1-SE, Mälardalen Real-Time Research Centre, Mälardalen University, April, 2008. Submitted to the 13th IEEE International Conference on Emerging Technologies and Factory Automation.

Paper F present the development of a plug-in framework for integration of real-time analysis methods in a commercial IDE for embedded real-time systems. The paper also present the integration, of two state of the art analysis techniques (i) response-time analysis for tasks with offsets and (ii) shared stack analysis, in the framework. The paper shows that the framework is well suited for integration of complex analysis methods, however, the paper shows that a considerable amount of modifications of analysis methods are needed to adapt them for industrial use due to differences in requirements and assumptions between industry and academia.

**Personal contribution:** Kaj was the main author of the paper. He was involved in all parts and responsible for specifying the requirements on the plug-in framework and to realize the analysis methods as plug-ins.

# 4.2 Impact of contributions

The contributions of this thesis have both industrial and scientific impact.

- From a scientific point of view, the contributions give researchers a picture of issues in transferring research results to industrial use. The thesis show that a considerable amount of work, addressing different issues, is needed to integrate results from academia to industry. In addition, the contributions in Paper E are highly relevant for the research community, in the sense that the paper presents methods to determine the possible preemption patterns in a system.

- From an industrial point of view, the thesis provides contributions on encapsulating novel real-time theory for efficient memory utilization, into methods and software engineering tools. This allows engineers to take advantage of the theories developed by the real-time research community. In general, the thesis provides means for development of predictable, memory efficient and reusable software based products. The results presented in the included papers, are implemented in a commercial tool suite called Rubus. The results will be available for developers with the upcoming release of the tool suite.

# Chapter 5

# **Conclusion and future work**

This thesis addresses the introduction of a memory efficient execution strategy, called stack sharing, in development of industrial embedded real-time systems.

The thesis shows, by an investigation of industrial requirements, that industrial embedded real-time systems need to support an increasing number of features with mixed real-time requirements. This requires predictable and efficient use of the computational resources in the systems. The thesis shows that this can be achieved by stack sharing. Stack sharing is a predictable and efficient execution strategy that reduces the memory consumption in systems, hence making it suitable for resource constrained real-time systems.

To achieve industrial use of stack sharing, the thesis presents a component model supporting stack sharing in development of embedded real-time systems with mixed real-time requirements. Furthermore, an integration of stack sharing in a real-time operating system is presented. The integration is presented in detail to highlight common issues in implementing execution models in a real-time operating system. The thesis also presents a novel analysis method for shared stack analysis. In an evaluation, the thesis show that the analysis method is both fast and that it gives tight bounds on the resulting stack usage, which makes it suitable for industrial use. The thesis presents the integration of the analysis method in an integrated development environment.

Altogether, the thesis presents both design and run-time techniques for efficient memory utilization in embedded real-time systems. The proposed techniques have clear scientific impact. Moreover, the techniques have been implemented in the Rubus tool suite. Rubus is currently used by a number of companies developing embedded real-time systems. With the upcoming release of the tool suite, the scientific results presented in this thesis will be available for developers using Rubus.

Several directions could be taken as future work. For instance:

- Even though it has been shown that stack sharing could theoretically reduce the memory utilization in systems, evaluating the memory reductions in a real-world setting still needs to be done. This would, amongst other things, reveal the actual applicability of stack sharing considering the restrictions (see Section 3.2) introduced by stack sharing.

- Reducing the pessimism of shared stack analysis methods could also be addressed as future work. The analysis method presented in this thesis requires worst case response times as input to the preemption analysis. The response time analysis could for example be extended to represent jitter as well as blocking more accurately. This would result in an improved shared stack analysis.

- Investigating how the preemption analysis, presented in paper E, can be applied in other contexts would be of interest. For example, it might be possible to extend the preemption analysis to support analysis of: (i) memory consumption in systems with dynamic memory allocation, (ii) cache usage, (iii) buffer requirements in synchronisation protocols.

# Bibliography

- [AB98] L. Abeni and G. Buttazzo. Integrating Multimedia Applications in Hard Real-Time Systems. In *Proceedings of the* 19<sup>th</sup> IEEE Real-Time Systems Symposium (RTSS'98), pages 4–13. IEEE Computer Society, Madrid, Spain, December 1998.

- [Abe98] L. Abeni. Server Mechanisms for Multimedia Applications. Technical Report RETIS TR98-01, Scuola Superiore S. Anna, Pisa, Italy, 1998.

- [ABRW91] N. Audsley, A. Burns, M. Richardson, and A. Wellings. Hard Real-Time Scheduling: The Deadline Monotonic Approach. In *Proceedings 8th IEEE Workshop on Real-Time Operating Systems and Software*, 1991.

- [Abs] Absint. Web page, http://www.absint.com/stackanalyzer/.

- [ABT<sup>+</sup>93] N.C. Audsley, A. Burns, K. Tindell, M.F. Richardson, and A.J. Wellings. Applying New Scheduling Theory to Static Priority Pre-emptive Scheduling. *Software Engineering Journal*, 8(5): 284–292, 1993.

- [Arc] Arcticus Systems. Web page, http://www.arcticus-systems.com.

- [Bak90] T.P. Baker. A Stack Based Resource Allocation Policy for Real-Time Processes. In *Proceedings of the 11th IEEE Real-Time Systems Symposium*. IEEE, 1990.

- [BBLB03] Scott Brandt, Scott Banachowski, Caixue Lin, and Timothy Bisson. Dynamic Integrated Scheduling of Hard Real-Time, Soft Real-Time, and Non-Real-Time Processes. In Proc. 24<sup>th</sup> IEEE

#### 30 Bibliography

*Real-Time Systems Symposium (RTSS).* IEEE Computer Society, December 2003.

- [BTW95] A. Burns, K. Tindell, and A Wellings. Effective Analysis for Engineering Real-Time Fixed Priority Schedulers. *IEEE Transactions on Software Engineering*, 22(5):475–480, May 1995.

- [But97] G.C. Buttazzo. *Hard Real-Time Computing Systems*. Kluwer Academic Publishers, 1997. ISBN 0-7923-9994-3.

- [BW96] A. Burns and A. Wellings. *Real-Time Systems and Programming Languages*, chapter 13.10.1 Immediate Ceiling Priority Inheritance. Addison-Wesley, second edition, 1996.

- [CMM<sup>+</sup>04] K. Chatterjee, D. Ma, R. Majumdar, T. Zhao, T.A. Henzinger, and J. Palsberg. Stack size analysis for interrupt-driven programs. *Inf. Comput.*, 194(2):144–174, 2004. ISSN 0890-5401.

- [CRM06] A. Crespo, I. Ripoll, and M. Masmano. Dynamic Memory Management for Embedded Real-Time Systems, volume 225 of IFIP International Federation for Information Processing. Springer, 2006.

- [Dig] Micro Digital. Web page, http://www.smxinfo.com/mt.htm.

- [DMT00] R. Davis, N. Merriam, and N. Tracey. How Embedded Applications using an RTOS can stay within On-chip Memory Limits. In *Proceedings of the WiP and Industrial Experience Session, Euromicro Conference on Real-Time Systems*, June 2000.

- [Ecl] Eclipse an open development platform. Web page, http://www.-eclipse.org/.

- [EHS97] A. Ermedahl, H. Hansson, and M. Sjödin. Response-Time Guarantees in ATM Networks. In Proc. 18<sup>th</sup> IEEE Real-Time Systems Symposium (RTSS), pages 274–284. IEEE Computer Society Press, December 1997. URL http://www.docs.uu.se/~ mic/papers.html.

- [Evi] Evidence Srl. Web page, http://www.evidence.eu.com.

- [GD07] R. Ghattas and A.G. Dean. Preemption Threshold Scheduling:Stack Optimality, Enhancements and Analysis. In *Proceedings of the 13th IEEE REal-Time and Embedded Technology and Applications Symposium*, April 2007.

- [GLN01] P. Gai, G. Lipari, and M. Di Natale. Minimizing Memory Utilization of Real-Time Task Sets in Single and Multi-Processor Systems-on-a-chip. In *Proceedings of the 22nd Real-Time Systems Symposium*. London, UK, Dec 2001.

- [HNN08] Hans Hansson, Mikael Nolin, and Thomas Nolte. Beating the Automotive Code Complexity Challenge. In National Workshop on High-Confidence Automotive Cyber-Physical Systems. Troy, Michigan, USA, April 2008.

- [KAS93] D.I. Katcher, H. Arakawa, and J.K. Strosnider. Engineering and Analysis of Fixed Priority Schedulers. *IEEE Transactions on* Software Engineering, 19(9):920–934, September 1993.

- [Leh90] J. Lehoczky. Fixed Priority Scheduling of Periodic Task Sets with Arbitrary Deadlines. In *Proc. 11<sup>th</sup> IEEE Real-Time Systems Symposium (RTSS)*, pages 201–212, December 1990.

- [Liu00] J. Liu. *Real-Time Systems*. Prentice Hall, 2000. ISBN 0-13-099651-3.

- [LL73] C. Liu and J. Layland. Scheduling Algorithms for Multiprogramming in a Hard-Real-Time Environment. *Journal of the ACM*, 20 (1):46–61, 1973.

- [LR03] R. Lencevicius and A. Ran. Can Fixed Priority Scheduling Work in Practice? In Proc. 24<sup>th</sup> IEEE Real-Time Systems Symposium (RTSS), page 358, December 2003.