IT Licentiate theses 2004-004 MRTC Report 2004/120

# On-Chip Monitoring for Non-Intrusive Hardware/Software Observability

MOHAMMED EL SHOBAKI

UPPSALA UNIVERSITY Department of Information Technology

### UPPSALA UNIVERSITET

### On-Chip Monitoring for Non-Intrusive Hardware/Software Observability

by Mohammed El Shobaki

September 2004

DIVISION OF COMPUTER SYSTEMS DEPARTMENT OF INFORMATION TECHNOLOGY UPPSALA UNIVERSITY UPPSALA SWEDEN

Dissertation for the degree of Licentiate of Technology in Computer Systems at Uppsala University 2004

### On-Chip Monitoring for Non-Intrusive Hardware/Software Observability

*Mohammed El Shobaki* mohammed.el.shobaki@mdh.se

Mälardalen Real-Time Research Center Department of Computer Science and Engineering Mälardalen University Box 883 SE-721 23 Västerås Sweden

http://www.mrtc.mdh.se/

http://www.idt.mdh.se/

© Mohammed El Shobaki 2004 ISSN 1404-5117 ISSN 1404-3041, ISRN MDH-MRTC-120/2004 Printed by Arkitektkopia, Västerås, Sweden Distributed by the Department of Information Technology, Uppsala University, Sweden, and the Department of Computer Science and Engineering, Mälardalen University, Sweden

This document was written in MS Word 2000, XEmacs 21.4, and typesetted in LATEX2e.

## Abstract

The increased complexity in today's state-of-the-art computer systems make them hard to analyse, test, and debug. Moreover, the advances in hardware technology give system designers enormous possibilities to explore hardware as a means to implement performance demanding functionality. We see examples of this trend in novel microprocessors, and Systems-on-Chip, that comprise reconfigurable logic allowing for hardware/software co-design. To succeed in developing computer systems based on these premises, it is paramount to have efficient design tools and methods.

An important aspect in the development process is observability, i.e., the ability to observe the system's behaviour at various levels of detail. These observations are required for many applications: when looking for design errors, during debugging, during performance assessments and fine-tuning of algorithms, for extraction of design data, and a lot more. In real-time systems, and computers that allow for concurrent process execution, the observability must be obtained without compromising the system's functional and timing behaviour.

In this thesis we propose a monitoring system that can be used for nonintrusive run-time observations of real-time and concurrent computer systems. The monitoring system, designated Multipurpose/Multiprocessor Application Monitor (MAMon), is based on a hardware probe unit (IPU) which is integrated with the observed system's hardware. The IPU collects process-level events from a hardware Real-Time Kernel (RTK), without perturbing the system, and transfers the events to an external computer for analysis, debugging, and visualisation. Moreover, the MAMon concept also features hybrid monitoring for collection of more fine-grained information, such as program instructions and data flows.

We describe MAMon's architecture, the implementation of two hardware prototypes, and validation of the prototypes in different case-studies. The main conclusion is that process level events can be traced non-intrusively by integrating the IPU with a hardware RTK. Furthermore, the IPU's small footprint makes it attractive for SoC designs, as it provides increased system observability at a low hardware cost.

To my father and my mother Taisir and Rahmeh for their never ending love, support and sacrifices

# Acknowledgments

This work would not have been possible without the support from many people whom I wish to thank. First, I would like to thank my dear supervisor Lennart Lindh, for giving me the opportunity to work for him and take me on as PhD Student. I've enjoyed working with you in many ways (not to forget our experiences together in preparing and selling fried herring during the summer festival in Västerås!). Second, I would like to sincerely thank Jan Gustafsson for taking the challenge to supervise me during the finishing of this work. You have been a source of inspiration, and I admire your dedication and patience with me. Third, I would like to thank Professor Hans Hansson, my main supervisor, for great reviewing and for monitoring my work actively, but non-interferingly!

I would also like to thank my colleagues and friends at the Computer Architecture Laboratory (CAL). Special thanks go to Joakim Adomat, for the creative discussions we've had throughout the years at the department, and also for designing many of the hardware prototypes I've used in my work. I'm also grateful to Johan Stärner for helping me with various issues regarding hardware design. Thanks Filip Sebek for your kind feedback on my work, and for making use of my research results in your own experiments – it has been valuable to me.

I would also like to acknowledge the efforts of the following people for their valuable support with implementing various parts of the software used in my work: Jeroen Heijmans, Andreas Malmquist, Adil Al-Wandi, Mehrdad Hessadi, Mladen Nikitovic, Johan Andersson and Toni Riutta.

Many thanks goes also to my fellow director of undergraduate studies, Åsa Lundkvist, and Monica Wasell, for backing me up during the final work with this thesis. Their support has been invaluable to me.

At the department where I work there are many people whom I wish to thank. It would be a bit impractical to list them all, even though I care for them all. There are however some people whom I wish to thank especially: Harriet Ekwall for creating such a homely working environment, Henrik Thane for constructive comments and ideas he had in relation to my initial work, and Thomas Larsson for the sincere moral support he has given me. I'm also indebted to my parents, my brothers and sisters, for the wonderful moral support they have given me. Sincere thanks goes also to my family-inlaw, the Masud family, for their wonderful support in many ways, including the nice meals and pastries they have stuffed me with during my stressful moments.

Last but not least, I'd like to give a huge virtual bunch of roses to my love in life, my wife Mouna, for her sweetness, devotion and support throughout my work. I love you!

This work has been financially supported by the KK Foundation, Vinnova (formerly Nutek), and Mälardalen University, for which I am very grateful.

Mohammed El Shobaki A beautiful day in September, 2004

#### vi

# Contents

| I | r    | Thesis                                      | 1             |

|---|------|---------------------------------------------|---------------|

| 1 | 1.1  | oduction Motivation                         | <b>3</b><br>4 |

|   | 1.2  | Thesis Outline                              | 5             |

| 2 | Bac  | kground                                     | 7             |

|   | 2.1  | Embedded and Real-Time Systems              | 7             |

|   |      | 2.1.1 Concurrency, Tasks, and Processes     | 9             |

|   |      | 2.1.2 Real-Time Operating Systems           | 9             |

|   |      | 2.1.3 Real-Time Kernel                      | 10            |

|   | 2.2  | Multiprocessor and Distributed Systems      | 10            |

|   | 2.3  | Testing, Debugging and Performance Analysis | 12            |

|   |      | 2.3.1 Debugging and Testing                 | 12            |

|   |      | 2.3.2 Performance Analysis                  | 12            |

|   | 2.4  | Monitoring                                  | 13            |

|   |      | 2.4.1 Monitoring Abstraction Levels         | 14            |

|   |      | 2.4.2 Types of Monitoring Systems           | 16            |

|   |      | 2.4.3 The Probe Effect                      | 20            |

| 3 | Prol | blem Formulation                            | 23            |

| 4 | Con  | tributions                                  | 25            |

| 5 | Sum  | imary of Papers                             | 29            |

| - | 5.1  | Summary of Paper A                          | 29            |

|   | 5.2  | Summary of Paper B                          | 30            |

|   | 5.3  | Summary of Paper C                          | 31            |

| 6 | Rela | nted Work                                   | 33            |

|   | 6.1  | Monitoring Real-Time Kernels                | 33            |

|   | 6.2  | Hardware Monitoring Systems                 | 35            |

|   | 6.3  | Hybrid Monitoring Systems                   | 39            |

|     | 6.4 On-Chip Techniques                                         | 40       |

|-----|----------------------------------------------------------------|----------|

| 7   | Conclusions                                                    | 43       |

| 8   | Future Work                                                    | 45       |

| Bil | bliography                                                     | 47       |

| II  | Included Papers                                                | 53       |

| 9   | Paper A:                                                       |          |

|     | A Hardware and Software Monitor for High-Level System-on-Chip  |          |

|     | Verification                                                   | 55       |

|     | 9.1 Introduction                                               | 57       |

|     | 9.2 MAMon                                                      | 59<br>60 |

|     | 9.2.1         The Probe Unit                                   | 60<br>62 |

|     | 9.2.3 The tool environment                                     | 63       |

|     | 9.3 An Ideal Example: Monitoring a Hardware Real-Time Kernel   | 64       |

|     | 9.4 Current and Further Work                                   | 65       |

|     | 9.5 Conclusions                                                | 66       |

|     | Bibliography                                                   | 66       |

|     |                                                                |          |

| 10  | Paper B:                                                       |          |

|     | On-Chip Monitoring of Single- and Multiprocessor Hardware Real | -        |

|     | Time Operating Systems                                         | 69       |

|     | 10.1 Introduction                                              | 71       |

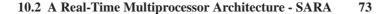

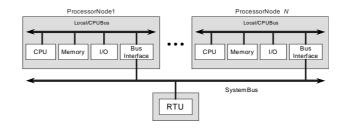

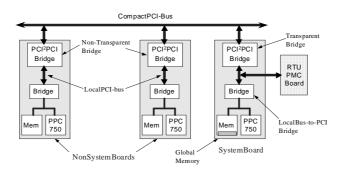

|     | 10.2 A Real-Time Multiprocessor Architecture - SARA            | 73       |

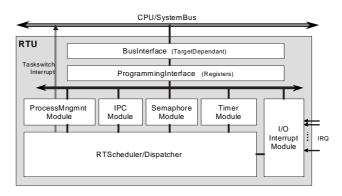

|     | 10.2.1 RTU - Real-Time Kernel in Hardware                      | 74       |

|     | 10.2.2 A SARA CompactPCI System                                | 75       |

|     | 10.3 A Monitoring System for Hardware-Accelerated RTOSs        | 76       |

|     | 10.3.1 Overview                                                | 76       |

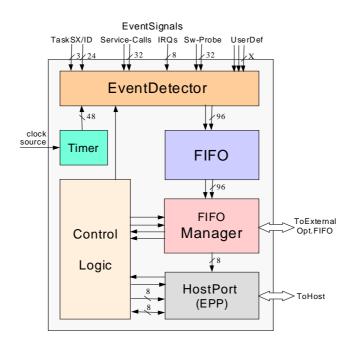

|     | 10.3.2 The Integrated Probe Unit                               | 77       |

|     | 10.3.3 Events                                                  | 80       |

|     | 10.3.4 Performance and FIFO Dimensioning                       | 81       |

|     | 10.3.5 The Monitoring Application Framework                    | 82       |

|     | 10.4 Physical Hardware Implementation                          | 84       |

|     | 10.4.1 The Hardware Prototype                                  | 85       |

|     | 10.4.2 Physical Footprint                                      | 85       |

\_\_\_\_

| Contents | ix |

|----------|----|

|          |    |

| 10.5 Prototype Evaluation                  | 86  |

|--------------------------------------------|-----|

| 10.6 Conclusions                           | 87  |

| Bibliography                               | 89  |

| 11 Paper C:                                |     |

| MAMon - A Multipurpose Application Monitor | 93  |

| 11.1 Introduction                          | 95  |

| 11.1.1 Related documents                   | 95  |

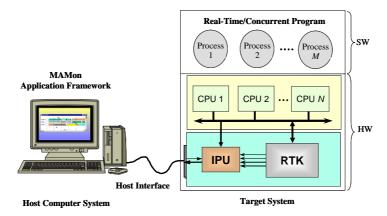

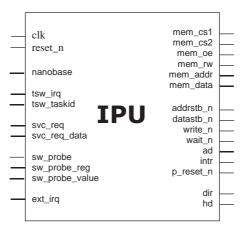

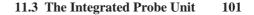

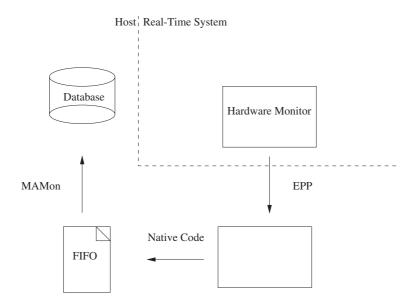

| 11.2 Overview of MAMon                     | 95  |

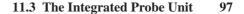

| 11.3 The Integrated Probe Unit             | 97  |

| 11.3.1 Entity interface                    | 97  |

| 11.3.2 The Host Interface                  | 99  |

| 11.4 The MAMon Application Framework       | 103 |

| 11.4.1 Connection with hardware            | 103 |

| 11.4.2 The main program                    | 103 |

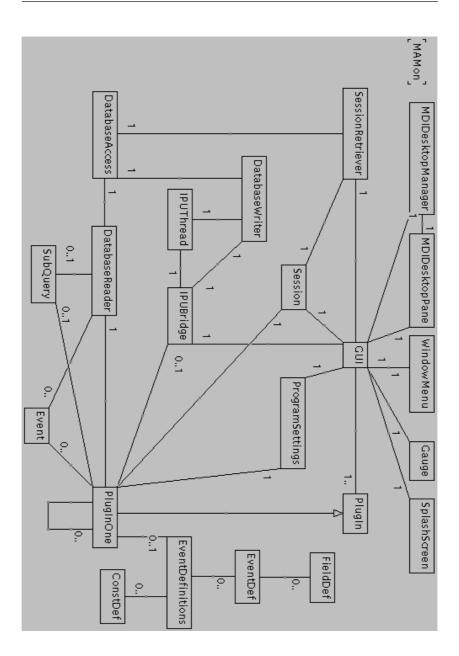

| 11.5 Framework Software Architecture       | 106 |

| 11.5.1 Packages                            | 106 |

| 11.5.2 Meeting requirements                | 106 |

| 11.5.3 Architecture Overview               | 109 |

| 11.5.4 The retrieval mechanism             | 112 |

| 11.6 Framework Programmer's Guide          | 117 |

| 11.6.1 General                             | 117 |

| 11.6.2 Adding a new plug-in                | 120 |

| 11.6.3 Using the event definitions file    | 125 |

| 11.6.4 Changing the DBMS                   | 125 |

| 11.6.5 Specific plug-ins                   | 126 |

| 11.7 MAMon Tool Desktop User Guide         | 128 |

| 11.7.1 Quick start                         | 128 |

| 11.7.2 Reference guide                     | 129 |

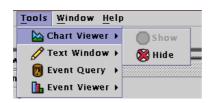

| 11.7.3 Plug-in Tools                       | 140 |

| Bibliography                               | 146 |

| A Patent                                   | 149 |

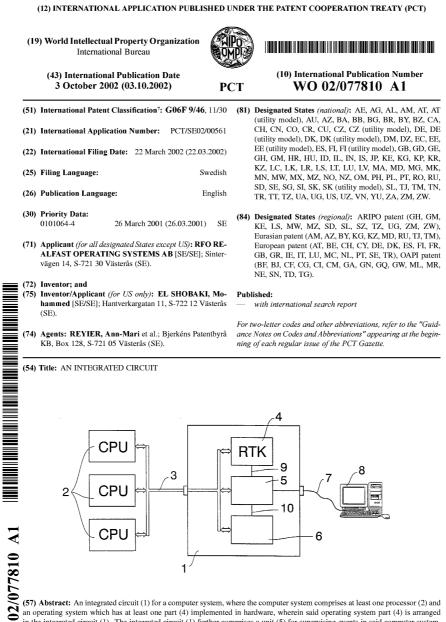

| A.1 Field of the invention                 | 153 |

| A.2 Prior art                              | 153 |

| A.3 Summary of the invention               | 154 |

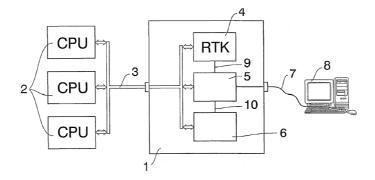

| A.4 Description of the drawings            | 156 |

| A.5 Description of embodiments             | 157 |

| A.6 Claims                                 |     |

| X | Contents |  |  |  |

|---|----------|--|--|--|

|   |          |  |  |  |

|   |          |  |  |  |

|   |          |  |  |  |

A.7 Drawings ..... 162

v

# List of Publications

This Licentiate<sup>1</sup> thesis is a summary of the following three papers. References to the papers will be made using the letters associated with the papers.

- A. Mohammed El Shobaki and Lennart Lindh, A Hardware and Software Monitor for High-Level System-on-Chip Verification, In proceedings of the IEEE International Symposium on Quality Electronic Design, San Jose, CA, USA, March 2001.

- **B.** Mohammed El Shobaki, On-Chip Monitoring of Single- and Multiprocessor Hardware Real-Time Operating Systems, In proceedings of the 8th International Conference on Real-Time Computing Systems and Applications (RTCSA), Tokyo, Japan, March 2002.

- C. Mohammed El Shobaki and Jeroen Heijmans, MAMon A Multipurpose Application Monitor, MRTC Report ISSN 1404-3041 ISRN MDH-MRTC-121/2004-1-SE, Mälardalen Real-Time Research Centre, Mälardalen University, Västerås, Sweden, September 2004.

Besides the above papers I have authored and co-authored the following scientific publications:

- Mohammed El Shobaki, Observability in Multiprocessor Real-Time Systems with Hardware/Software Co-Simulation, In Swedish National Real-Time Conference SNART'99, Linköping, Sweden, August 1999.

- II. Mohammed El Shobaki, Verification of Embedded Real-Time Systems using Hardware/Software Co-simulation, In proceedings of the 24th Euromicro Conference, Vol. I, pp. 46-50, Västerås, Sweden, August 1998.

- III. Lennart Lindh, Johan Stärner, Johan Furunäs, Joakim Adomat, and Mohammed El Shobaki, Hardware Accelerator for Single and Multiprocessor Real-Time Operating Systems, In Seventh Swedish Workshop on Computer Systems Architecture, Chalmers, Göteborg, Sweden, June 1998.

<sup>&</sup>lt;sup>1</sup>A Licentiate degree is a swedish degree halfway between MSc and PhD.

Ι

# Thesis

1

## Chapter 1

# Introduction

As human beings we strive for comfort and easy living. Therefore we build advanced devices and machines that can automate hard duties. As humans we need to communicate with each other and we need to be entertained. Therefore we build telecommunication systems, television, home cinema, and computer games. To discover far places and meet other people we need to travel. Therefore we build automobiles, ships and air craft. In almost each of these inventions by the modern human we can find computer systems, that is, intelligent pieces of electronics that do what we program them to do. Thus, our everyday lives are becoming increasingly more dependant on these systems, and we take for granted that they work properly and safely.

As a concrete example, take for instance the features of a modern car. Figure 1.1 illustrates features that typically utilize a computer, for example, the engine control computer that optimize performance and fuel combustion, the computer that detects collisions and activate the airbags in the event of a crash, the computer that regulates the interior climate based on passenger preferences and exterior climate conditions, the computer that controls the braking system for maximum efficiency, and more. In fact, a modern car may contain up to a 100 computer systems that together orchestrate all these features.

Figure 1.1: Example of features of a modern car

This thesis is about methods for observing the behaviour of a computer system. These observations are necessary for a number of reasons, including the need for testing and optimisation during the development of computer systems. The thesis proposes a concept for carrying out certain types of observations without disturbing the natural behaviour of the observed computer, for reasons which will be discussed in the following chapters.

In Section 1.1 we will present the overall motivations for this work, and in Section 1.2 we outline the thesis contents.

### 1.1 Motivation

Today's computer-based products are complex and require extensive efforts to design and test. They are complex because they comprise many components, complex software and hardware, and features a lot of functionality. This is a trend which is clearly seen in the consumer electronics market, and in state-ofthe-art industrial systems. The development of these products tends to be as challenging as it is increasingly time-consuming, expensive, and error-prone. Therefore, the developers need to cut down the development time and improve quality, which in turn, demands better tools and development methodologies.

One important aspect in the development process is *observability*, i.e., the ability to observe the system's behaviour at various abstraction levels in the design. These observations are required for many reasons, for instance, when looking for design errors, during debugging, during optimisation of algorithms, for extraction of design data, and a lot more. Observability is however not an issue restricted to development purposes only, it may also be necessary after the deployment of products as well, e.g., for error recovery, for surveillance

issues, for collection of statistical measurements (e.g. concerning the use of a product), etc.

We characterize the quality of observability as: *good* (or high) if the system allows for detailed and accurate analysis of all of its components, and *poor* (or low) if the system is obstructive and hard to analyse confidently.

In essence, this thesis is motivated by the needs from industry in seeking better observability for complex computer systems based on state-of-the-art hardware and software architectures.

### 1.2 Thesis Outline

The thesis is divided into two parts, where the first part (part I) gives an introduction to the research area, describes the research problems, presents the thesis contributions, conclusions, etc. More specifically: Chapter 2 lays the background which the subsequent discussions will proceed from. Chapter 3 presents the problems we have focused on. In Chapter 4 we present the main contributions of this work. Chapter 5 summarises the papers included in the second part of the thesis. In Chapter 6 we present relevant related work. Chapter 7 presents the thesis conclusions, and in Chapter 8 we give some directions on future work.

In the second part (part II) of the thesis we have appended the included papers, Paper A - C.

Finally, in the appendix we have enclosed a Swedish-registered patent that constitutes one of our contributions (described in Chapter 4).

# Chapter 2

## Background

This chapter presents the basic concepts used in the thesis. The concepts and their related terms will be assumed to be familiar to the reader in the discussions throughout the thesis.

### 2.1 Embedded and Real-Time Systems

An *embedded system* is typically a product which includes a computing system. The product is said to "embed" the computing system inside. Embedded system do not necessarily look like computers, however it is typical that embedded systems interact with their environment. For instance, a mobile phone is regarded an embedded system: it reacts on incoming calls, user input, cell roaming, etc. A talking doll is another example, since the doll might express a message based on which part of its body, or button, has been pushed, or if it gives a response to a playing child's voice.

A real-time system is a system that interacts with its environment in a timely constrained manner. The real-time system must produce results within specified time limits. A computation result (or actuation) must be delivered neither too late, nor too early. The criticality of violated timing constraints, or *missed execution deadlines*, classifies real-time systems into *hard* or *soft* real-time systems [But97]. Timing failures in a hard real-time system are considered haz-ardous and very critical and should never be allowed. Examples on hard real-time requirements can be found in automotive and avionic systems, medical equipment, military systems, energy and nuclear plant control systems. On the contrary, the requirements in soft real-time systems are not so critical and may

tolerate timing constraint violations, either by discarding the produced results or by allowing a degraded quality. Soft real-time requirements can be found in telecommunication systems, audio and video applications, streaming media, airline reservation systems, etc.

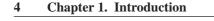

A typical real-time system (see Figure 2.1) consists of a controlling subsystem (the computer), and the controlled subsystem (the physical environment). The interactions between the two subsystems can be described by three main operations:

- Sampling

- Processing

- Responding

The computer subsystem continuously samples data from the physical environment. Sampled data is then immediately processed by the computer subsystem, and a proper response is sent to the physical environment. All three operations must be performed within the required timing constraints. For example, it is imperative that an air bag control system in an automobile responds within set timing constraints in the event of a crash. The response must neither be too late (being non-effective), or too early (risking hazardous manoeuvring of the car).

Figure 2.1: A real-time system

#### 2.1 Embedded and Real-Time Systems

9

#### 2.1.1 Concurrency, Tasks, and Processes

The real-time computing software is in its simplest form implemented as one big program loop. Typically, such programs can be found in *Programmable Logic Controllers* (PLCs) which are used to control relatively simple (industrial) applications [NSMT+00]. PLC programs are often realised as loops that include instructions to read input data (e.g. from sensors), perform logical processing on the input, and write out data (e.g. to actuators or relays).

When the controlled environment is more complex, the real-time software may need to be divided into several *tasks*. A task, also called *thread*, is an independent sequence of program instructions which may execute concurrently with other tasks (multitasking) on the same real-time computer. Tasks execute under the control of a *Real-Time Operating System* (see below) which also manages the computer resources (processor and memory), inter-task communication, synchronisation, and I/O. Tasks normally share the memory space – both instructions and data – with other tasks. The shared memory is typically also used for communication and synchronisation with other tasks.

A software *process* is a special case of a task which have an own protected memory space, i.e. it does not share memory with other processes. The process may be seen as a standalone program acting as though it owns the computer for itself. Moreover, a process may internally be represented by one or more concurrent tasks that share execution within the process. Memory-protection between processes is usually implemented using a hardware *memory management unit* (MMU) which checks accesses to privileged memory. Whenever processes needs to communicate (*Inter-Process Communication*), messages must be passed via the RTOS (using *message-passing*) which normally hides copying of message data between processes' memory space.

From now on the terms *task* and *process* will be used interchangeably in the text, unless they are explicitly distinguished.

#### 2.1.2 Real-Time Operating Systems

A *Real-Time Operating System* (RTOS) is an operating system specially intended for real-time systems, that allows easier design, execution, and maintenance of real-time systems and applications. The use of an RTOS simplifies the design process by providing the developer with a uniform programming interface to the underlying computer hardware. In this way, the developer may focus on designing the application rather than bothering about the details and structure of the computer hardware. The main responsibility of an RTOS during run-time is to manage the available computing resources so that application

tasks may share, and synchronise their use of, these resources in a way that timeliness is ensured. Timeliness is ensured by *scheduling* (see Section 2.1.3), which is the main technique used to guarantee availability of resources at the right time to the tasks.

Another responsibility of an RTOS is the management of communication between processes, and synchronisation of resource utilisation. A process that wants to communicate a message to another process usually does this by invocating a system-call to the RTOS which then takes care of data copying and notification of message arrival to the addressed process(es). In the case of resource synchronisation, the RTOS typically administrates certain data structures (*mailboxes, queues, mutexes, semaphores*, etc. [Lab02]) that organises process admission to the shared resources.

#### 2.1.3 Real-Time Kernel

The core of an RTOS is the *Real-Time Kernel* (RTK). This component manages the scheduling of process execution on the available CPU-resources in the system. In single-processor systems the processes will *time-share* the same processor, and in a multiprocessor system the processes will be distributed over the processors. The time-shared execution follows a *scheduling scheme* which is tailored to fit the design requirements. For instance, one scheduling scheme is that every process should get equal time shares for execution. Another scheme may be that processes execute based on their *priority*, i.e., the process with highest priority is allowed to execute before processes with lower priorities. There are also schemes that follow execution schedules that are defined pre-run-time, so-called *static schedules*, which contains activation times (*absolute* or *relative time*) for each process [Liu00]. The RTK may also be responsible for the scheduling of other resources than the CPU [Lab02].

A typical RTK is implemented in software as part of the RTOS. There exist however implementations of the RTK in hardware [Lin92, AFLS96, MRS<sup>+</sup>90, NUI<sup>+</sup>95] (described also in the included papers of Part II). The main benefit with hardware-implemented RTKs is that they execute in parallel with the CPU(s) in the system, i.e. like a *co-processor*, which results in a performance acceleration of the RTOS' operation in some type of systems [Fur00].

### 2.2 Multiprocessor and Distributed Systems

Over the past years we have seen a trend towards parallel computing as opposed to single processor systems. There are several reasons for this trend, including

#### 2.2 Multiprocessor and Distributed Systems 11

the following:

- Physical speed limit Processor manufacturing is facing physical limits such as line-widths on silicon, limit in speed of light (high frequencies), signal quality, etc.

- Special purpose processing In some systems it is better to partition and distribute a computation over a set of special purpose processors, rather than using one general-purpose processor. For example, a 3D graphics computation is best done using an array processor and a DSP rather than using a general CPU.

- Fault tolerance and availability By increasing the number of processing elements, computer systems can be made more fault-tolerant in the event of failures.

- The Internet There is no doubt that the Internet has greatly contributed to the demand for higher performance and throughput in communication applications. Large database systems are today a big market for multiprocessing.

Designing multiprocessor systems and applications is however not trivial, and requires deep understanding of parallelism and problems related to concurrency. When a program is partitioned into portions that are allowed to execute in parallel, i.e. processes, it is usually necessary to communicate data between them in order to fulfil a computation. This inter-process communication usually requires synchronisation of the involved parts. For instance, a *process A* that intends to read a message from *process B* must be synchronised with the availability of the message from *process B*. The typical errors in multiprocessor systems are particularly related to communication and synchronisation [Gai86].

There are various meanings for what is to be considered a multiprocessor system. Some texts depend their definition on the communication media between the processors, e.g. shared-memory, distributed memory, or communication over a network. Other texts rely the definition on the usage of a common (global) clock. In the latter meaning, a system with different clocks (one for each processor) is considered a distributed system. In this text the definition is; *if two or more processing elements are used in a computation of a program, it is considered a multiprocessor system.* Hence, we do not distinguish between the terms multiprocessor and distributed systems.

### 2.3 Testing, Debugging and Performance Analysis

### 2.3.1 Debugging and Testing

Debugging, as defined in the ANSI/IEEE standard glossary of software engineering terms [MH89], is "the process of locating, analysing, and correcting suspected faults". A fault is defined to be the direct cause of some error. Since the occurrence of errors can have different reasons, they are usually not predictable, and therefore we must locate them using *debuggers*. A debugger is a tool which helps the designer to examine suspected errors in a program, and eventually also remedy the errors. The term *cyclical debugging* is commonly used to describe debugging as an iterative process, in which the debugger is used to find and correct errors, over and over again, until no more errors can be found.

Testing and debugging are similar activities with respect to finding errors. However, testing is more of an automated process of exposing different input to the system under test, and evaluating its results (output). The objective is to find input data, or patterns of data, that cause erroneous results [SVS<sup>+</sup>88]. The faults that are found during the testing process are then put under observation in a debugger.

In real-time systems, errors may also occur in the time-domain. Real-time systems are therefore harder to debug than non-real-time systems. The ability to track down timing-related errors was largely an unexplored area until the early 1980's. Glass (in [Gla80]) reported a significant lack of effective tools in the emergence of real-time systems development and referred to the problem as the *"lost world"* of software testing and debugging. Today, various debugging systems and methods have been developed in order to address timing-related issues [TFC90a, JRR94, TSHP03].

#### 2.3.2 Performance Analysis

While removal of errors is an important part of the design process, others are implementation optimisation and fine-tuning of algorithms. To pursue such activities the designer needs to analyse behaviour and performance of the developed system, its components and sub-components. Performance analysis is of importance to find performance bottlenecks, and to extract design-parameters such as execution times, response times, communication delays of various kind, and so on. The extraction of design-parameters is for instance valuable to task scheduling analysis and estimates for resource allocation.

In the next section we will describe how testing, debugging and performance

#### 2.4 Monitoring 13

analysis may be facilitated through the use of *monitoring*.

### 2.4 Monitoring

Monitoring is *the process of gathering information about a system* [TBHS96, MH89]. We gather information which normally cannot be obtained by studying the program code only. The collected information may be used for program testing, debugging, task scheduling analysis, resource dimensioning, performance analysis, fine-tuning and optimisation of algorithms. The applicability of monitoring is wide, and so is the spectrum of available monitoring techniques. In this section we give a general presentation of a monitor, and describe different monitoring systems, the type of information collected by monitors, and the problem-related issues with monitoring.

In essence, a monitor works in two steps: *detection* (or triggering) and recording. The first operation refers to the process of detecting the object of interest. This is usually performed by a trigger object that is inserted in the system, which when executed, or gets activated, indicates an event of interest for recording. The latter operation, recording, is the process of collecting events and saving them in buffer memory, or communicate them to external computer systems for the purpose of further analysis or debugging. An event is a record of information which usually constitutes the object of interest together with some additional meta data regarding that object (e.g. the time when the object was recorded, the object's source address, task/process ID, CPU node, etc.). The type of monitored objects depend on the level of abstraction which the user is interested in. Section 2.4.1 below describes different abstraction levels that are associated with program execution. The trigger object may be an instruction, or a function, that is inserted in the software. It may also be a physical sensor, or probe, connected with physical wires in the hardware, such as CPU address, data, and control buses.

An important issue regarding the monitoring process is the amount of *execution interference* that may be introduced in the observed system due to the involved operations of a monitor. This execution interference, or *perturbation*, is unwanted because it may alter the true behaviour of the observed system, in particular such systems that are inherently timing-sensitive such as real-time and distributed systems. We will return to this issue in the discussion on *probe-effects* in Section 2.4.3.

#### 2.4.1 Monitoring Abstraction Levels

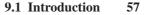

Software execution may be monitored at different levels of abstraction as the information of interest is different in levels of detail. Higher-level information refers to events such as inter-process communication and synchronisation. In contrast, lower-level information refers to events such as the step-by-step execution trace of a process. The execution data collected at the process level includes the process state transitions, communication and synchronisation interactions among the software processes, and the interaction between the software processes and the external process. The execution data collected at the function level includes the interactions among the functions or procedures within a process. The user can isolate faults within functions using the function-level execution data. In this section, the different levels of abstraction in software execution are identified.

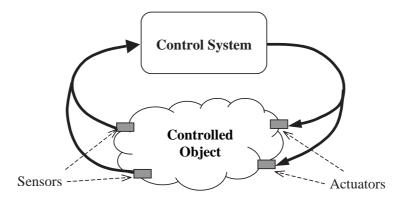

#### 2.4.1.1 System Level

The system-level may be seen as the user's, or the real-world, view of the computer system. It abstracts away all implementation details and only provides information that is relevant to the system's user (or to the real-world process). For instance, the *press* of a button in a car's instrument board, and the *activation/deactivation* of the car's *Traction Control System* (anti-spinning system) feature, would be considered as system-level events (see Figure 2.2). This level of information is normally useful for system-test engineers during the final steps in the development process.

Figure 2.2: Monitoring at the system level of abstraction

#### 2.4 Monitoring 15

#### 2.4.1.2 Process and OS Level

To monitor program execution at the process level, we consider a process as a black box which can be in of the three states: *running, ready, or waiting*. A process changes its state depending on its currents state and the current events in the system. These events include interactions among the processes and the interactions between the software processes and the real world. The events that directly affect the program execution at the process level are distinguished from those events that affect the execution at lower levels. Assigning a value to a variable, arithmetic operations, and procedure calls, for instance, are events that will not cause immediate state changes of the running process. Inter-process communication and synchronisation are events that may change a process' running status and affect its execution behaviour. The following events are typically considered as process level events:

- Process Creation

- Process Termination

- Process State Changes

- Process Synchronisation

- Inter-process Communication

- External Interrupts

- I/O Operations

#### 2.4.1.3 Functional Level

The goal of monitoring program execution at the function level is to localise faulty functions (or procedures) within a process. At this level of abstraction, functions are the basic units of the program model. Each function is viewed as a black box that interacts with others by calling them or being called by them with a set of parameters as arguments. So the events of interest are function calls and returns. The key values for these events are the parameters passed between functions.

#### 2.4.1.4 Instruction Level

The instructional level of abstraction refers to the step-by-step execution of CPU-instructions. It is, from a software perspective, regarded as the lowest

level of abstraction of a program for a modern  $CPU^1$ . To monitor each executed instruction is, however, a heavy duty on any monitor since it requires at least the CPU-performance of the system being observed, and the collected amounts of event traces are too huge to be of practical use. Instead, it is sufficient enough to monitor just those instructions that affect the execution path of a program, e.g. conditional branches, traps, exceptions, etc. Using this information in combination with the software's source, or object code, it is possible to reconstruct the execution behaviour. For many programs<sup>2</sup>, such a method reduces the amount of recorded data with several orders of magnitude.

#### 2.4.2 Types of Monitoring Systems

Monitoring systems for software or system-level analysis are typically classified into three types: 1) *software monitoring systems*, 2) *hardware monitoring systems*, and 3) *hybrid monitoring systems*. In the following we will describe each type of system. Chapter 6 gives a more detailed presentation of monitoring systems that relates to our work on hardware and hybrid monitoring.

#### 2.4.2.1 Software Monitoring Systems

In this category of monitoring systems, only software is used to instrument, record, and collect information about software execution. Software monitoring systems offer the cheapest and most flexible solution where a common technique is to insert instrumentation code at interesting points in the target software. When the instrumentation code is executed the monitoring process is triggered and information of interest is captured into trace buffers in target system memory. The drawbacks of instrumentation is the utilisation of target resources such as memory space and processor execution time.

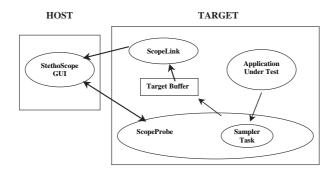

Below is a more detailed description of a specific monitoring tool, called *StethoScope*, which serves as an example on how a typical software monitor operates.

#### StethoScope

StethoScope [Baw99] by Real-Time Innovations Inc. is a commercially avail-

<sup>&</sup>lt;sup>1</sup>In earlier days an instruction was seen as a composition of sub-instructions, called microcode, which together carried out the different operations that occur inside the CPU-core (e.g. memory load/store operation, register shifts, ALU-operations and bit-tests, etc). Today however, micro-coding is rarely done by software designers, though there exists application specific CPUs that allows micro-coding.

<sup>&</sup>lt;sup>2</sup>It is widely known that many programs spend (very roughly) 90% of their time in about 10of their code; 10% of static instructions account for 90% of dynamic instructions.

able tool for monitoring real-time systems. The monitoring process is claimed to be non-intrusive since the sampling of the system is limited to only reading variables from the application memory. Their definition of non-intrusive monitoring means, however, that the application software does not require modification.

StethoScope comprise a set of monitoring tasks on the target, and a GUI on a host computer, see Figure 2.3. The monitoring tasks are compiled and linked together with the application. During program execution, the *Sampler Task* periodically awakes and copies the currently monitored variables (denoted *signals* in the GUI) from their addresses in the application to the *Target Buffer*. Later the *ScopeLink daemon* copies the Target buffer to the GUI's *Live Buffer*. The user can at any time, via the StethoScope GUI, choose the signals (variables) that will be monitored, and change data collection parameters, for example the rate at which data is collected. Such requests are handled by the *ScopeProbe daemon* which in turn updates internal data structures that control the monitoring process.

Figure 2.3: The components of StethoScope's architecture (ref. [Stetho-Scope1999])

The execution of the application is of course disturbed during the periodical copying of memory. ScopeProbe's Sampler task runs at the highest priority and needs to interrupt the application to perform its copying function. Thus, StethoScope's monitoring process cannot be claimed to be non-intrusive in the sense we have discussed in the previous section. However, StethoScope calls this *non-intrusive asynchronous* monitoring. It is asynchronous in the sense that samples are taken at specific time intervals, i.e. they are not co-ordinated

with the events in the program. For example, variables can be assigned values several times (e.g. in a loop) between each invocation of the Sampler task. This way of monitoring is also said to be *discontinuous*. Another disadvantage with StethoScope's asynchronous monitoring is that it can only sample static or global variables. Stack variables may be out of scope when the sampling occurs.

In order to monitor stack variables, the StethoScope system offers a synchronous monitoring model which, however, requires instrumented code. The instrumented code has calls to StethoScope's ScopeProbe API inserted at the locations where synchronous sampling is required. A call to the API function *ScopeCollectSignals()* will force sampling to occur in the same scope (immediately). Thus, stack variables can be monitored. The advantages with synchronous monitoring are precise control of sampling relative to program events and consistent data, since the variables are always sampled at the same point in the program.

#### 2.4.2.2 Hardware Monitoring Systems

In this category of monitoring systems, only hardware (custom or general) is used to perform detection, recording and collection of information regarding the software. For this to work, the target system must lend itself for observations by external means (the monitoring hardware).

The primary objective of hardware monitoring is to avoid, or at least minimize, interference with the execution of the target system. A hardware monitoring system is typically separated from the target system, and thus, does not use any of the target system's resources. Execution of the target software is monitored using passive hardware (or probes) connected to the system buses and signals. In this manner, no instrumentation of the program code is necessary. Hardware monitoring is especially useful for monitoring real-time and distributed systems since changes in the program execution time are avoided.

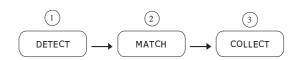

In general, the operation of monitoring hardware can be described by the three steps (see Figure 2.4): *event detection, event matching*, and *event collection*. In the first step, detection, the hardware monitor listens continuously on the signals. In the second step, the signal samples are compared with a predefined pattern which defines what to be considered as events. When a sample matches an event-pattern, the process triggers the final step, collection, where the sampled data is collected and saved. The saved samples may be stored locally in the monitoring hardware, or be transferred to a host computer system where usually more storage capacity can be obtained.

Apart from the advantage of avoiding target interference, are the typical

Figure 2.4: Hardware monitoring steps

precision and accuracy of hardware monitors. Since the sole duty of a hardware monitor is to perform monitoring activities (usually at equal or higher system speed than the target's) the risks of loosing samples are minimized.

A disadvantage of hardware monitors is their dependency on the target's architecture. The hardware interfaces, and the interpretation of the monitored data must be tailored for each target architecture it is to be used in. Thus, monitoring solutions using hardware are more expensive than software alternatives. Moreover, a hardware monitor may not be available for a particular target, or takes time to customize, which may increase the costs further in terms of delayed development time.

Another problem with hardware is the integration and miniaturisation of components and signals in today's chips which renders difficulties in reaching information of interest, e.g. cache-memory, internal registers and buses, and other on-chip logic. To route all internal signals out from a chip may be impossible because of limited pin counts.

In general, hardware monitoring is used to monitor either hardware devices or software modules. Monitoring hardware devices can be useful in performance analysis and finding bottlenecks in e.g. caches (accesses/misses), memory latency, CPU execution time, I/O requests and responses, interrupt latency, etc. Software is generally monitored for debugging purposes or to examine bottlenecks, load-balancing (degree of parallelism in concurrent and multiprocessor systems), and deadlocks.

#### 2.4.2.3 Hybrid Monitoring Systems

Hybrid monitoring uses a combination of software and hardware monitoring and is typically used to reduce the impact of software instrumentation alone. A hardware monitor device is usually attached to the system in some way, e.g. to a processor's address/data bus, or on a network, and is made accessible for instrumentation code that is inserted in the software. The instrumentation is typically realised as code that extracts the information of interest, e.g. variable data, function parameters, etc., which is then sent to the monitor hardware.

For instance, if the monitor hardware has memory-mapped registers in the system, the instrumentation would perform data store operations on the monitor's memory-addresses. The hardware then proceeds with event processing, filtering, time-stamping, etc., and then communicates the collected events to an external computer system. This latter part typically resembles the operation of a pure hardware monitor. The insertion of instrumentation code also resembles the technique used in a software monitoring system; i.e. it can either be done manually by the programmer, automated by a monitoring control application or by compiler directives.

#### 2.4.3 The Probe Effect

Instrumentation of programs, also called "probing", is convenient because it is a general method which technically is applicable in many systems. For concurrent programs however, the delay that is introduced by the insertion of additional instructions may alter the behaviour of the program. The *probeeffect*, which originates from *Heisenberg's Uncertainty Principle*<sup>3</sup> applied to programs [Gai86, MH89], may result in that either a non-functioning concurrent program works with inserted delays, or a functioning program stops working when the inserted delays are removed. This can also be seen as a difference between the behaviour of a system being tested and the same system not being tested. Typical errors related to the probe-effect are synchronisation errors in regions containing critical races for resources [Gai86].

Not only may concurrent programs suffer from the probe-effect, but also real-time systems are concerned since they are inherently sensitive to timing disturbances, especially if deadlines are set too tight (i.e. non or low-relaxed worst-case execution times). Consequently, distributed/parallel real-time systems are most sensitive to probe-effects. This is one important reason why testing and debugging (using monitoring) of real-time systems (particularly distributed real-time systems) is so difficult [Tha99, TBHS96, MH89]. Hence, probe-effects must be avoided in the development of real-time systems. There are basically three approaches to eliminate the probe-effect:

• *Leave the probes in the final system*. In this approach the probes that have been used during development are left in the final product. This way we

<sup>&</sup>lt;sup>3</sup>Bugs that relate from probe-effects are in some texts referred to as "Heisenbugs" after the Heisenberg Uncertainty Principle from physics. This principle state that the instrumentation used to measure something, no matter how non-intrusive one may think it is, will always perturb the object being measured and result in an inaccurate measurement.

#### 2.4 Monitoring 21

avoid behavioural changes due to removal of probes. The disadvantage is of course that the final system may suffer from inferior performance.

- *Include probe-delays in schedulability analysis.* In real-time systems design it is straightforward to include the probes in the execution time of the program, i.e. dedicate resources (execution time, memory, etc) to probes. However, this method does not guarantee the ordering of events, it only provides enough execution time to compensate for the inserted delays.

- Use non-intrusive hardware. Bus-snoopers and logic analysers are typical examples of passive hardware which do not interfere with the system. Other techniques are the use of multi-port memories, reflective memory, and use of special hardware. There are also hybrid monitoring systems which utilise hardware support together with software instrumentation. The disadvantage of this solution may be higher development and product costs due to extra hardware.

## **Problem Formulation**

In the previous chapter we have discussed the necessity of observability of the components of computer systems, during development and after deployment. We will now describe our main research problems in terms of three central questions that the thesis will provide answers to.

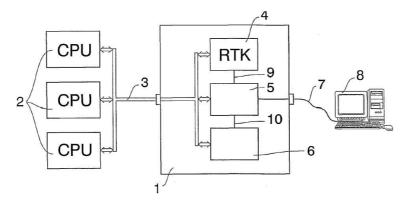

In our research group we are interested in exploiting the use of hardware parallelism to improve performance, as well as the determinism, of RTOS functions in real-time computers. As a result of this research we have developed several hardware implementations of an RTK [AFLS96, LSF<sup>+</sup>98, LKF99], with various features that range from simple priority-based task-scheduling for single-processor systems, to support scheduling, IPC, and interrupt management, for multiprocessor systems. In realising these systems we encountered difficulties in tracking down bugs that appeared at run-time, mainly because it was nearly impossible to determine if the bugs where located in the hardware RTK, or in the software that made use of it. Moreover, for the same reasons as when tracking bugs, it was not straightforward to analyse the system's performance and the possible execution speed-ups with hardware-acceleration. These struggles led us to the formulation of the first question:

**Question 1** (Q1). *How can we observe, analyse, and visualize the run-time behaviour of processes in single- and multiprocessor computer systems that employ a hardware RTK?*

Note that in Q1 we focus only on the run-time behaviour, i.e. we are not interested in observing a simulated model of the system. We also discard so-

#### 24 Chapter 3. Problem Formulation

lutions that imply restricted, or lowered, execution speeds. This latter requirement rules out emulation systems and logic analysers, since they typically do not allow for full execution speeds [Ref till ngn känd survey :)].

The following question is related to Q1 in that a solution to the observation problem should not result in an altered behaviour of the system, or a change of the system's timing characteristics. The answer to this question is in fact the same as providing a solution to Q1 without introducing probe-effects (see Chapter 2). The question is justified because there exists attempts to utilise software tasks (special monitor/debug tasks) that polls the hardware contents of the RTK via its register interface. Hence, we formulate the second question as follows:

**Question 2** (Q2). *Can we develop a solution to Q1 without perturbing the functional behaviour and timing properties of the observed system?*

The answers to Q1 and Q2 respectively are provided in Contribution A and B, and partly through Contribution E (see Chapter 4).

While Q1 and Q2 only concerns observations at the process-level, i.e. such information that would only require monitoring the hardware RTK, we still need to address observations of the software at abstraction levels other than just the process-level. For instance, how can we track a software process' function-call hierarchy, or how to monitor data variables, or the execution of a particular instruction? In certain cases it might also be necessary to sample register contents in a CPU, an act which is not obvious without software instrumentation, or special hardware support in the CPU. Employing a hardware monitor which passively listens to a CPU's address and data buses may be inadequate, or even useless, if the CPU is equipped with an instruction and/or data cache - which today is more or less typical rather than exceptional. Therefore, with this background, it is motivated to formulate the following question:

**Question 3** (Q3). *Is it possible to monitor software execution and data, at any abstraction level, in a solution to both Q1 and Q2?*

The answer to Q3 is also given in Contribution A and B, and Contributions C and D respectively provides a validation of that answer.

## Contributions

In this chapter we will briefly describe the main contributions presented in this thesis.

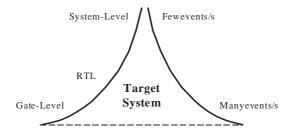

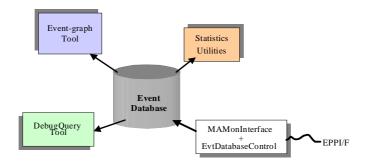

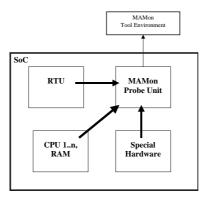

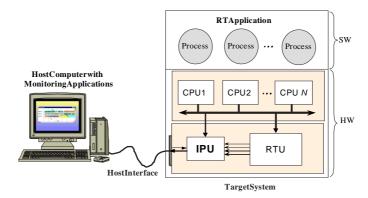

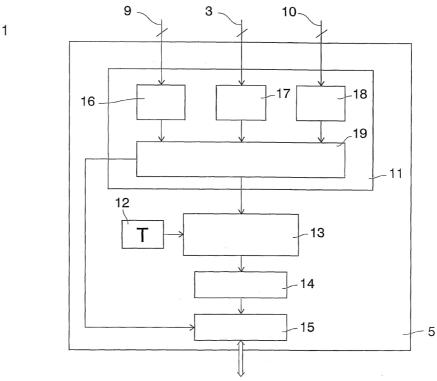

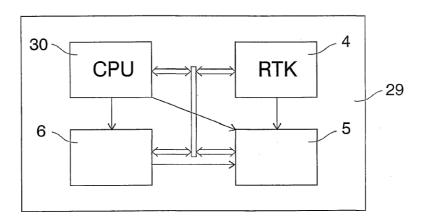

#### Contribution A: Concept of a Uniform Hardware/Software Monitor

Our central contribution is the concept of a monitoring system that can be applied for observations of a computer system's hardware and software components. This monitoring system, designated *Multipurpose/Multiprocessor Application Monitor* (MAMon), is based on an integrated hardware probe unit (IPU) which is integrated with the observed system's hardware. The IPU collects events of interest in the system, and transfers them out of the system to a dedicated computer where the events can be analysed without perturbing the observed system's behaviour. In the case where the observed system incorporates a hardware RTK component, the IPU may also be connected to that component's internal signals and data structures in order to extract process-level information.

The main advantages with the MAMon concept are:

- a) detection and collection of events occurs non-intrusively to the system, or with a minimum of impact should the software require instrumentation for hybrid monitoring,

- b) hardware and software events are monitored using the same device i.e. uniform monitoring is achieved – and are displayed and analysed using the same monitor applications and tools, and

#### 26 Chapter 4. Contributions

c) the IPU may be implemented as an IP-component for integration in a SoC, thus overcoming the difficulties related to probing obstructive hardware.

In Paper A we introduce the MAMon concept from a verification of SoCs perspective, and in Paper B the ideas are refined for more general applicability. Paper B also describes the integration with the RTK in more detail, and gives an overall architectural description of the monitoring system.

Contributions B through D presented below are validations of the MAMon concept for various system configurations and applications. It should be mentioned that MAMon has been applied in a HW/SW co-simulation model of a SoC comprising a CPU (an ISS-model of a PowerPC 60x), an RTK, and the monitor's IPU. However, this configuration is not documented or validated thoroughly, hence, it is not listed as a contribution of its own.

#### Contribution B: A Monitor for a Multiprocessor System

The second contribution, presented in Paper B, is an implementation of MAMon for a real-time multiprocessor based on *commercial-off-the-shelf* (COTS) hardware. This multiprocessor system is a research platform built for studies on hardware-acceleration for RTOSs [LKF99, KL99]. Our aim is to build a monitor that is able to observe the behaviour of multiprocessing software run by a hardware-accelerated RTOS, i.e. a hardware RTK.

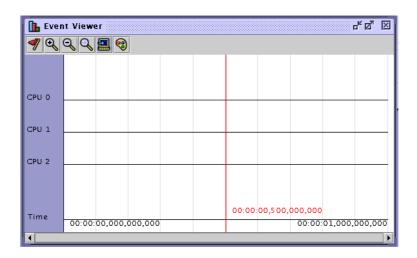

The implementation resulted in a hardware prototype based on a FPGA (a Xilinx Virtex-1000) that is configured with the hardware RTK and the monitor's IPU. Using the monitor in combination with the RTK we are able to analyse the software's behaviour at the task-level, running on up to three CPUs. The analysis is done with no intrusion on the system's behaviour or timing. With an addition of instrumentation of the software it is also possible to utilise the monitor in a hybrid manner, with a cost per *instrumentation probe* reduced to the time-length of a 32-bit bus write cycle (in this case a PCI-bus@33 MHz).

In Paper B we present the full details of the implementation, and describe the tools we also developed to control the monitoring process and analyse collected data (see Contribution E below).

#### Contribution C: A Monitor for a Single-Processor System

In another validation of our monitor we were interested in studying the performance differences between a single-processor system running a hardwareaccelerated RTOS [Fur00] and a software-only RTOS, called *SW Symo* [Riz01]. The idea was to compare the amount of idle execution time (i.e. when no tasks are running) for the same software when run on each system, an experiment which would reveal the execution overhead imposed by the RTOS. The experiment involved adaptation of the hardware IPU – used in the multiprocessor system in Contribution B – with the ability to detect currently executing tasks managed by the SW Symo RTOS. The task id:s are extracted using instrumentation of the SW Symo's context-switch routine, so that the currently active task's id is written to a memory-mapped register in the IPU (i.e. an IPU software probe register).

The experiment was part of a master thesis project, carried out by Al-Wandi and Hessadi [AWH02], under supervision of the authour of this thesis. They also designed two graphical interface tools that visualise CPU work load in the studied systems; one tool to visualise *live* CPU work load (i.e. CPU utilization), and the other tool to show *historical* CPU load (see Contribution E below). Due to their limited project time they managed, however, only to finish the experiments with the SW Symo target system.

#### Contribution D: A Hybrid Monitor for Cache Performance Analysis

In [Seb02a], Sebek used the hybrid monitoring feature of the monitor (described in Contribution B) in order to analyse cache behaviour in a real-time system. Sebek's objective was to measure the *execution delay* that relates from task pre-emption in a multitasking single-processor system [SG02, Seb02b]. Using the built-in performance monitors in a MPC750 CPU [Mot97], he was able to construct software which reads cache-related performance properties, and by using the monitor's time-stamp function he also measured execution times in order to determine the *cache-related pre-emption delay* (CRPD) as well as the *threshold miss-ratio* values for an instruction cache. Thus, his solution to minimise software overhead was to write the cache-related data to dedicated *software probe registers* in the IPU. The IPU collected the data, and packaged it into "software probe" events which were time-stamped and sent further to an external PC where the data was analysed.

Using our monitor, Sebek was able to measure very accurately, and analyse, the CRPD in a real-time system.

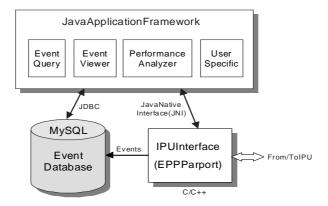

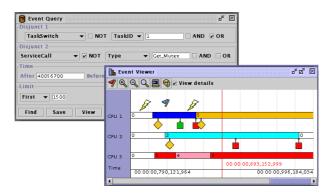

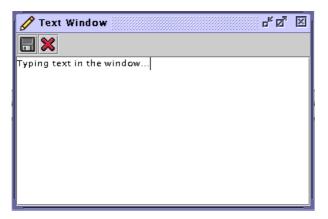

#### Contribution E: A Framework for Monitoring Applications and Tools

To make use of the collected events from the monitor, e.g. for analysis and visualisation purposes, we developed an application platform that enables easy and rapid design of customised monitor tools (see Paper B and Paper C). This platform, which is based on a modular design implemented using the JAVA object-oriented language, provides support for communication with the IPU

#### 28 Chapter 4. Contributions

(i.e. hardware driver), a relational (SQL) database for structured and welldefined storage/access of the collected events, and a GUI environment for user interaction with the monitor and visualisation of collected events. Initially, the platform constituted only a tool to graphically depict events collected from a SoC comprising one CPU and a RTK (described in Paper A). In the following work, presented in Paper B, the platform was developed to become a framework with more general applicability.

The usability of the framework was validated also in the work by Al-Wandi and Hessadi [AWH02] who implemented tools that visualise CPU work load (see Contribution C). We have also extended the framework with support for USB-communication with the IPU. This latter effort was carried out by Andreas Malmquist [Mal04] under supervision of the author of this thesis.

In Paper C we give a more comprehensive documentation of the framework, its components, and the tools it currently supports.

#### **Contribution F: Patent**

Our final contribution is a patent on the MAMon concept described in contributions A through D. The patent, which currently is registered in Sweden (patent no **SE517917**), was acquired by *RealFast AB*; a company specialised in developing IP-components for the FPGA and SoC market. Their motivation for acquiring and exploiting a patent based on our ideas shows an industrial relevance, and an interest in our work. A valid and registered patent also gives a proof of uniqueness since it has been reviewed by patent engineers and patent registration authorities.

The patent application was authored in co-operation with *Ann-Marie Reyier* at *Bjerkéns Patentbyrå* in Västerås, Sweden. Mrs Reyier wrote the application based on our documentation and pre-published papers. For reference, we have included the patent description and its claims in Appendix A.

### **Summary of Papers**

### 5.1 Summary of Paper A

Mohammed El Shobaki and Lennart Lindh, A Hardware and Software Monitor for High-Level System-on-Chip Verification, In proceedings of the IEEE International Symposium on Quality Electronic Design, San Jose, CA, USA, March 2001.

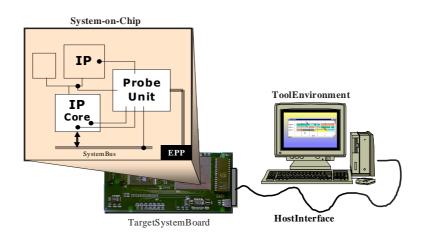

Summary: The paper describes our concept of an on-chip hardware monitor for uniform monitoring of hardware/software systems-on-chip (SoC). For hardware analysis the monitor detects and collects events at the register-transfer level (RTL), performing very much like a logic analyser. For software analysis the monitor may be attached to processing elements in the SoC, e.g. to processor interconnects and buses, in order to extract software instructions and data. In this latter sense the monitor works non-intrusively to the system, or with a minimum of interference if the software is instrumented for hybrid monitoring. In the paper we also relate to our previous work on hardware-implemented Real-Time Kernels, and discuss how such an implementation may be integrated with the monitor in order to extract process-level events without perturbing a system's functional, timing, and performance behaviour. This property is required especially when debugging and analysing SoCs used in real-time systems. We also motivate the use of the monitor in a top-down debugging strategy where it can be employed in the early stages of verification and validation at a system or process level, and later, at the hardware's RTL whenever more level of detail is requested. Finally, the paper describes the embryo to a full-

#### **30** Chapter 5. Summary of Papers

featured monitoring application framework with support for monitor control, event tracing, and visualisation of performance and data.

*My contribution:* The paper is written by me, under supervision of Lennart Lindh.

### 5.2 Summary of Paper B

Mohammed El Shobaki, On-Chip Monitoring of Single- and Multiprocessor Hardware Real-Time Operating Systems, In proceedings of the 8th International Conference on Real-Time Computing Systems and Applications (RTCSA), Tokyo, Japan, March 2002.

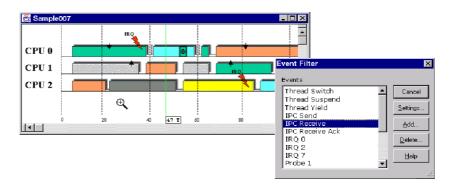

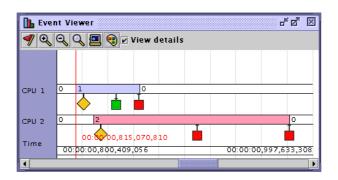

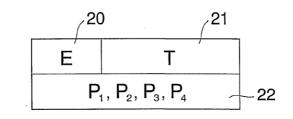

*Summary:* The paper presents further developments to the concepts discussed in Paper A, and describes a physical implementation of a prototype monitor along with a much more developed version of the framework for monitoring applications. The monitor hardware is realised in a *probe unit* (IPU) that is integrated with a hardware RTK in an FPGA-chip, which in turn is mounted on a PCI-board in a *commercial-off-the-shelf* multiprocessor system. In this setup the RTK manages real-time process scheduling for up to three CPU-boards hosting PowerPC 60x/75x processors. The monitor, which has probes tightly coupled to the RTK's data paths, logs all scheduling events in the RTK, as well as its other features, e.g. inter-process communication events, semaphore state transition events, external interrupts, etc. The logged events are time-stamped and then transferred through a dedicated connection to an external PC, where the events are stored in a relational database, ready to be accessed by monitoring applications.

The software that access collected events, or controls the monitor, are implemented as separate modules which are plugged into a GUI-platform developed using Java. The paper describes the architecture of this GUI-platform, which we choose to call a *framework* since it is designed to be easily customisable and upgradeable.

Moreover, the paper demonstrates the use of the monitoring system and presents some implementation data. The paper's main conclusion is that it is possible to non-interferingly observe the behaviour of software processes by monitoring the hardware RTK.

*My contribution:* I'm the sole author of the paper.

#### 5.3 Summary of Paper C 31

### 5.3 Summary of Paper C

Mohammed El Shobaki and Jeroen Heijmans, MAMon - A Multipurpose Application Monitor, MRTC Report ISSN 1404-3041 ISRN MDH-MRTC-121/2004-1-SE, Mälardalen Real-Time Research Centre, Mälardalen University, Västerås, Sweden, September 2004.

*Summary:* This report describes the architecture and integral components of the Multipurpose Application Monitor (MAMon). The IPU's signal interface is described and we explain how the interface conforms to intregation with a hardware RTK and the communication port to an external host computer. The report also provide a programmer guide for the monitoring application framework, as well as a user manual for the currently implemented monitoring tools within the framework. The report is mainly intented as a reference guide for working with MAMon at a user's level.

*My contribution:* I compiled this paper based on several documents, partly written by me and partly by my co-author, Mr Heijmans. Mr Heijmans contributed to the implementation of MAMon's host software, an effort which he conducted in a special student project under my supervision.

## **Related Work**

This chapter presents academic research and industrial practice that relate to our work. We will first give an overview of the related work, then present some of the surveyed systems more in detail, and give a discussion on their relation to our contributions. For more extensive surveys on monitoring systems see [TBHS96] and [Sch94].

First, we must emphasize that MAMon is primarily a process-level monitor for systems employing a hardware RTK, and secondary it is a multipurpose hybrid monitor in that it can also be used to record software-generated events. These two features may be combined in an embodiment of the monitor, but may also be used separately. For simplicity we differentiate between the two features in the following discussions. Section 6.1 presents related work on monitoring RTKs, Section 6.2 describe work on hardware-only monitoring systems, and Section 6.3 presents work on hybrid monitoring systems. Finally, in Section 6.4 we relate our contributions to on-chip techniques that has emerged with the developments towards hardware/software co-design and systems-on-chip.

### 6.1 Monitoring Real-Time Kernels

To our knowledge, our research on monitoring hardware-implemented RTKs is unique. We believe this is mainly due to limited research efforts on hardware RTKs. However, for software-implemented RTKs there exists a number of proposed systems. For a few examples see [TKM89, TFC90a, Win04, Men98b]

#### 34 Chapter 6. Related Work

#### The ARTS monitor

In [TKM89], Tokuda et al. presents a research prototype on a real-time monitor developed for the ARTS distributed operating system. The proposed monitor requires support from ARTS kernel such as notification of process' state-changes, e.g. process creation, waking-up from a blocked state, being scheduled, etc. The events collected from the target system are sent to a remote host for display of the execution history.

#### The ''Imitating'' Monitor

The work by Tsai et al. in [TFC90b, TFC90a] presents a more generic realtime hardware monitor which is suitable for observations at various abstraction levels, including the *process-level*. This monitor is realised as a separate computer system that is attached to the buses of the computer under observation, and utilise bus-snooping in order to reflect the observed system's state onto the monitoring system. Thus, the monitor *imitates* the execution at the observed system. We discuss this monitor further in the next section.

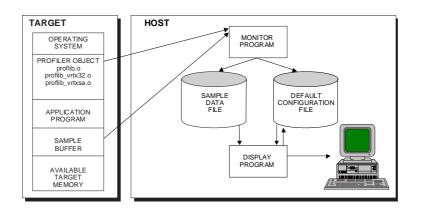

#### **Xpert Profiler**

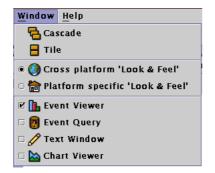

*Xpert Profiler* by Mentor Graphics [Men98b] is a typical commercially available tool for profiling, measurement, and evaluation of software written for the VRTX RTOS [Men98a]. Xpert Profiler relies on software-instrumentation that may be automatically inserted in the RTOS kernel whenever task-switching activities are to be monitored. The monitoring process is controlled by a program on separate host computer (see Figure 6.1), where the recorded data is also visualised and processed. On the target side, the application is linked with the libraries (*proflib.o* and *proflib\_vrtxsa/vrtx32.o*) containing service-routines that can be called (either by the RTK or the application) at the instances where samples are requested. The sample buffer, which also resides on the target side, contains the samples that are collected during a monitoring session.

*Discussion:* The main difference between MAMon and the above described systems is the notification of events which for the surveyed systems (except the Imitating monitor) require instrumentation of the software RTKs, while in MAMon the kernel-events are sampled directly from a hardware RTK. In case of the ARTS monitor the intrusiveness due to the software instrumentation is included in the schedulability analysis. The commercial monitors, like Xpert Profiler [Men98b] and its equals, do not take any measures to eliminate execution interference or probe-effects.

Figure 6.1: The components of Xpert Profiler [Men98b].

### 6.2 Hardware Monitoring Systems

#### The Bus-listener and The Imitating Monitor

Research prototypes on hardware-supported monitoring for single-processor systems can be found in the work by Plattner [Pla84], and Tsai et al. [TFC90b]. Common techniques in these approaches are to employ bus-listeners to reflect memory-accesses onto a separate memory system, and the use of imitating processors, i.e. in order to perform intrusive monitoring on a (non-intrusively) reflected system. For instance, Plattner's monitor, called *bus listener*, is attached to the target processor's buses in order to detect memory transactions which then are reflected onto a separate memory designated *phantom memory*. From this memory it is then possible to examine the system's state without interfering with the observed system. Tsai et al.'s monitor is also attached to the processor buses, however, the detected signal activities are used to synchronise a separate computer node (with an own processor, memory system, and I/O-devices). This computer node imitates the observed computer, and allows for examination of the system state without interference with the monitored system.

#### The Interrupt Priority Level Monitor

In [JC91], Baker and Crilly presents an architecture for monitoring interrupt priority levels on an interrupt-driven processor. The monitor is used to exter-

#### 36 Chapter 6. Related Work

nally observe the interrupt levels at which the processor execute and the time spent at each priority level in order to determine processor and service-routine efficiency. The concept is proposed for a generic interrupt-driven microprocessor, and presumes that information on interrupt activities can be extracted offchip via the processor bus-interface.

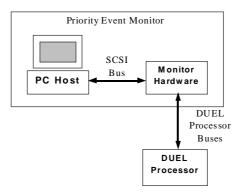

Figure 6.2 shows an overview of the monitoring system for a generic target processor called DUEL. The monitor hardware observes the DUEL processor for interrupts, log events, and buffer event records. The SCSI bus is used for host control of the monitor hardware, and for sending event records to the host for post-analysis. The host system controls the monitor hardware, collects event records, and reconstructs the event history for use with analysis tools.

Figure 6.2: Baker and Crilly's Priority Event Monitor [JC91]

#### The Ted Monitor

In yet another related work, Liu and Parthasarathi [LP89] presents a hardware monitor for a shared-memory multiprocessor system called *Ted* (Testbed for Distributed Processing). They propose this monitor to be used in debugging and run-time process-scheduling. In the following we will describe this monitor in detail to give a more complete presentation of a work that relates to the multiprocessor implementation of MAMon (presented in Paper B).

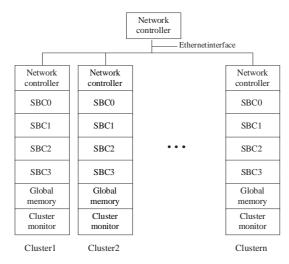

The Ted consists of Intel 8086 single board computers that are organised in clusters. Within a cluster, the single board computers are connected to a *Multibus* and communicate via shared memory. Clusters are connected with an Ethernet network. Figure 6.3 shows the architecture of Ted. The monitoring

hardware is attached via a probe interface to the Multibus on the cluster to be monitored. In this approach, the monitoring device detects events on the Multibus and collects the data for use by an external system. The external system may be a completely independent computer, or it could be one of the board computers (dedicated for monitoring) within the cluster as is proposed by the authors. In the latter case, the monitor is controlled via the Multibus, hence, a slight interference will occur. However, when monitored data is collected from the monitor, the parallel port of the processor board is used in order to avoid contentions on the Multibus.

Figure 6.3: The Ted architecture [LP89]

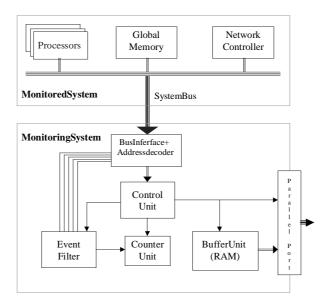

Figure 6.4 shows the internal architecture of the monitoring device. The probes of the monitor connects to the bus within the cluster. A standard Multibus edge connector serves this function. Via the monitor's bus interface, the bus signals are sampled and compared with a set of predefined signal patterns. This is done in the event filter where a set of user-programmable registers contains the patterns for the events of interest. The bit pattern consists of the following signal lines:

- 20-bit address lines

- 16-bit data lines, and

#### 38 Chapter 6. Related Work

#### • 4-bit read/write lines (I/O and memory r/w)

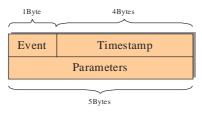

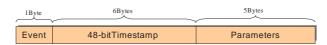

Figure 6.4: Functional block diagram of the Ted monitor [LP89]