Mälardalen University Press Dissertations No. 347

## SPACE COMPUTING USING COTS HETEROGENEOUS PLATFORMS

#### INTELLIGENT ON-BOARD DATA PROCESSING IN SPACE SYSTEMS

Nandinbaatar Tsog

2021

School of Innovation, Design and Engineering

Copyright © Nandinbaatar Tsog, 2021 ISBN 978-91-7485-528-9 ISSN 1651-4238 Printed by E-Print AB, Stockholm, Sweden

## Abstract

Space computing is growing due to the technological advances of high performance commercial off-the-shelf (COTS) computing platforms. Space offers a complex and challenging environment, with size, weight, power, and timing constraints, communication limitations, and radiation effects.

The research presented in this thesis aims at investigating and supporting intelligent on-board data processing using COTS heterogeneous computing platforms in space systems. We investigate platforms with at least one Central Processing Unit (CPU) and one Graphics Processing Unit (GPU) on the same chip. The main goal of the research presented in this thesis is twofold. First, investigate the heterogeneous computing platforms to propose a solution to tackle the above-mentioned challenges in space systems. Second, to complement the proposed solution with novel scheduling techniques for real-time applications that run on COTS heterogeneous platforms in harsh environments like space.

The proposed solutions are based on the system model that considers the use of alternative executions of parallel segments of tasks. Although offloading a parallel segment to a parallel computation unit (such as GPU) improves the best-case execution times of most applications, it can increase the response times of tasks in some applications due to the overuse of GPU. Hence, using the proposed task model can be a key to decreasing the response times of tasks and improving schedulability of the system. The server-based scheduling techniques support the proposed task model by guaranteeing the execution slot for parallel segments on CPU(s). Our experimental evaluation shows that the proposed allocation can increase the number of schedulable task sets of the real-time systems up to 90% compared to the static allocation of applications.

We also present a dynamic allocation method using server-based scheduling with the proposed task model that can improve the schedulability up to 16%. Finally, the thesis presents a simulation tool that supports designers in choosing heterogeneous processing units using the proposed task model while considering the different levels of radiation tolerance to the processing units.

# Sammanfattning

Rymddatorn växer på grund av de tekniska framstegen inom högpresterande kommersiella plattformar (COTS). Rymden erbjuder en komplex och utmanande miljö med storlek, vikt, effekt och tidsbegränsningar, kommunikationsbegränsningar och strålningseffekter.

Forskningen som presenteras i denna avhandling syftar till att undersöka och stödja intelligent omborddatabehandling med hjälp av COTS heterogena datorplattformar i rymdsystem. Vi undersöker plattformar med minst en Central Processing Unit (CPU) och en Graphics Processing Unit (GPU) på samma chip. Huvudmålet med forskningen som presenteras i denna avhandling är tvåfaldigt. Undersök först de heterogena dataplattformarna för att föreslå en lösning för att hantera ovan nämnda utmaningar i rymdsystem. För det andra, för att komplettera den föreslagna lösningen med nya schemaläggningstekniker för realtidsapplikationer som körs på COTS heterogena plattformar i tuffa miljöer som rymden.

De föreslagna lösningarna baseras på systemmodellen som överväger användningen av alternativa utföranden av parallella segment av uppgifter. Även om avlastning av ett parallellt segment till en parallell beräkningsenhet (t.ex. GPU) förbättrar de bästa tillämpningstiderna för de flesta applikationer, kan det öka svarstiderna för uppgifter i vissa applikationer på grund av överanvändning av GPU. Därför kan användning av den föreslagna uppgiftsmodellen vara en nyckel för att minska responstiderna för uppgifter och förbättra systemets schemaläggning. De serverbaserade schemaläggningsteknikerna stöder den föreslagna uppgiftsmodellen genom att garantera exekveringsplatsen för parallella segment på CPU(er). Vår experimentella utvärdering visar att den föreslagna fördelningen kan öka antalet schemalagda uppgiftsuppsättningar för realtidssystemen upp till 90% jämfört med den statiska fördelningen av applikationer.

Vi presenterar också en dynamisk allokeringsmetod med hjälp av serverbaserad schemaläggning med den föreslagna uppgiftsmodellen som kan förbättra schemaläggningen upp till 16%. Slutligen presenterar avhandlingen ett simuleringsverktyg som stöder konstruktörer i att välja heterogena bearbetningsenheter med hjälp av den föreslagna uppgiftsmodellen samtidigt som man beaktar de olika strålningstoleransnivåerna för behandlingsenheterna.

To my family.

Where there's a will there's a way

# Acknowledgments

First of all, I would like to express my sincere gratitude to my supervisors, my principal supervisor Professor Mikael Sjödin, industrial co-supervisor, Adjunct Professor Fredrik Bruhn, academic co-supervisors Professor Moris Behnam and Associate Professor Saad Mubeen. I am glad that I could travel this journey with you under your expert guidance, persistent support, and enormous encouragement. I am grateful for your valuable ideas, guidance, suggestions, comments, and feedback.

I appreciate the contributors, Dr. Matthias Becker and Dr. Harris Gasparakis, to this thesis. Many thanks to all of my co-authors for collaborating with me. Thank you Jakob Danielsson, Marcus Larsson, Ashalatha Kunnappilly, Dr. Mobyen Uddin Ahmed, Dr. Shahina Begum, Alexandros Binios, Dr. Jaan Praks, and Dr. René Laufer.

Special thanks to Jakob, who is my friend, colleague, bro, contributor, psychologist, room&team-mate, our team-leader, my driver, etc. It is not only a matter of time. "Admire, respect, support, sharpening, help" these words describe you.

I appreciate Dr. Guillermo Rodriguez-Navas, who is my friend and advisor. Thanks for spending many days for discussing, leading, consolidating the ideas. I hope we will work together more and more.

I deeply appreciate my teachers, Sharaa, Munkhjargal, Erdene Natsagdorj, Professor Motomu Takeshige, Professor Shimizu, and Professor Yasushi Kato. Your words supported me to coming back to the academia.

I would like to thank Prof. Sasikumar Punnekkat and Prof. Masoud Daneshtalab for valuable suggestions and comments on the thesis and dissertation.

Special thanks to my friends and advisors, Jakob Danielsson, Marcus Larsson, Tobias Andersson, Uyanga Ganbaatar, Batbuyan Batchuluun, Dr. Guillermo Rodriguez-Navas, Dr. Predrag Filipovikj, Filip Markovic, Ashalatha Kunnappilly, Mirgita Frasheri, Dr. Gabriel Campeanu, Leo Hatvani, Dr. Momo, Dr. Svetlana Girs, Prof. Kristina Lundqvist, Prof. Cristina Seceleanu, Prof. Masoud Daneshtalab, Prof. Micke, Dr. Sara Abbaspour, Prof. Tiberiu Seceleanu, Dr. Marcus Jägemar, Stefan Karlsson, Aldin Berisa, Zenepe Satka, Tugu, Batya, Mitsuteru Kaneoka, Koji Yamaguchi, and Prof. Ryu Funase. Your words, cheered me up a lot.

```

1 if ($id =~ /([a-z][a-z][0-9][0-9])/) {

2     print <<MDH;

3     To $1,

4     Thank you for spending time with me at MDH.

5     MDH

6 }</pre>

```

I appreciate the DPAC project for funding my doctoral study. I also appreciate Advanced Micro Devices, Inc. (AMD) and Unibap AB (publ.) for donating and providing the test platforms. In addition, I am thankful to Volvo CE, Saab, and SaraniaSat Inc. for providing the test data. Furthermore, I would like to thank TESO Corporation, MOOCHA co-authors, DPAC members, HERO project team members, and family members.

Finally and foremost, I would like to express my greatest gratitude to my wife Bolormaa, son Ananda, parents, sister Nandin, and Jouni for your continuous love, support, and encouragement.

Nandinbaatar Tsog Sala, Oct 12, 2021

## **List of Publications**

### **Papers Included in the Doctoral Thesis**<sup>1</sup>

- Paper A: Intelligent Data Processing using In-Orbit Advanced Algorithms on Heterogeneous System Architecture – Nandinbaatar Tsog, Moris Behnam, Mikael Sjödin, Fredrik Bruhn. In the Proceedings of the 39th International IEEE Aerospace Conference, AeroConf 2018.

- Paper B: A Trade-Off between Computing Power and Energy Consumption of On-Board Data Processing in GPU Accelerated In-Orbit Space Systems

Nandinbaatar Tsog, Saad Mubeen, Mikael Sjödin, Fredrik Bruhn. In the Transactions of the Japan Society for Aeronautical and Space Sciences, Aerospace Technology Japan, ATJ 2020.

- Paper C: Enabling Radiation Tolerant Heterogeneous GPU-based Onboard Data Processing in Space – Fredrik C. Bruhn, Nandinbaatar Tsog, Fabian Kunkel, Oskar Flordal, Ian Troxel. In the CEAS Space Journal, CEAS 2020.

- Paper D: Simulation and Analysis of In-Orbit Applications under Radiation Effects on COTS Platforms – Nandinbaatar Tsog, Saad Mubeen, Mikael Sjödin, Fredrik Bruhn. In the Proceedings of the 42nd International IEEE Aerospace Conference, AeroConf 2021.

- Paper E: Static Allocation of Parallel Tasks to Improve Schedulability in CPU-GPU Heterogeneous Real-Time Systems – Nandinbaatar Tsog, Matthias Becker, Fredrik Bruhn, Moris Behnam, Mikael Sjödin. In the Proceedings of the 45th Annual Conference of the IEEE Industrial Electronics Society, IECON 2019.

- Paper F: Offloading Accelerator-intensive Workloads in CPU-GPU Heterogeneous Processors – Nandinbaatar Tsog, Saad Mubeen, Fredrik Bruhn,

<sup>&</sup>lt;sup>1</sup>The included papers have been reformatted to comply with the doctoral thesis settings.

xiv

Moris Behnam, Mikael Sjödin. In the Proceedings of the 26th International Conference on Emerging Technologies and Factory Automation, ETFA 2021.

# Additional Peer-Reviewed Publications, not Included in the Doctoral Thesis

- A Trade-Off between Computing Power and Energy Consumption of On-Board Data Processing in GPU Accelerated Real-Time Systems – Nandinbaatar Tsog, Mikael Sjödin, Fredrik Bruhn. In the Proceedings of the 32nd International Symposium on Space Technology and Science, ISTS 2019.

- Using Docker in Process Level Isolation for Heterogeneous Computing on GPU Accelerated On-Board Data Processing Systems – Nandinbaatar Tsog, Mikael Sjödin, Fredrik Bruhn. In the Proceedings of the 12th IAA Symposium on Small Satellites for Earth Observation, IAASmallSat 2019.

- 3. Moon Cubesat Hazard Assessment (MOOCHA) An International Earth-Moon Small Satellite Constellation - Alexandros Binios, Janis Dalbins, Sean Haslam, Rusnė Ivaškevičiūtė, Ayush Jain, Maarit Kinnari, Joosep Kivastik, Fiona Leverone, Juuso Mikkola, Ervin Oro, Laura Ruusmann, Janis Sate, Hector-Andreas Stavrakakis, Nandinbaatar Tsog, Karin Pai, Jaan Praks, René Laufer. In the Proceedings of the 12th IAA Symposium on Small Satellites for Earth Observation, IAASmallSat 2019.

- Using Heterogeneous Computing on GPU Accelerated Systems to Advance On-Board Data Processing - Nandinbaatar Tsog, Mikael Sjödin, Fredrik Bruhn. In the European Workshop on On-Board Data Processing, OBDP 2019.

- A Systematic Mapping Study on Real-time Cloud Services Jakob Danielsson, Nandinbaatar Tsog, Ashalatha Kunnappilly. In the Proceedings of the 1st Workshop on Quality Assurance in the Context of Cloud Computing, QA3C 2018.

- 6. Advancing On-Board Big Data Processing Using Heterogeneous System Architecture - Nandinbaatar Tsog, Mikael Sjödin, Fredrik Bruhn. In the Proceedings of the ESA/CNES 4S Symposium 2018, 4S 2018.

- Real-Time Capabilities of HSA Compliant COTS Platforms Nandinbaatar Tsog, Matthias Becker, Marcus Larsson, Fredrik Bruhn, Moris Behnam, Mikael Sjödin. In the Proceedings of the 37th IEEE Real-Time Systems Symposium (WiP), WiP RTSS 2016.

# Contents

| Ι | Thesis       |                                               |    |  |  |

|---|--------------|-----------------------------------------------|----|--|--|

| 1 | Introduction |                                               |    |  |  |

|   | 1.1          | Thesis Goal and Research Challenges           | 4  |  |  |

|   | 1.2          | Outline of the Thesis                         | 5  |  |  |

| 2 | Bac          | kground                                       | 7  |  |  |

|   | 2.1          | Space Computing                               | 7  |  |  |

|   |              | 2.1.1 On-Board Data Processing                | 7  |  |  |

|   |              | 2.1.2 Radiation Effects                       | 9  |  |  |

|   | 2.2          | Heterogeneous Computing                       | 9  |  |  |

|   |              | 2.2.1 Heterogeneous Architectures             | 10 |  |  |

|   |              | 2.2.2 Memory Model & Interconnection          | 12 |  |  |

|   |              | 2.2.3 Heterogeneous System Architecture (HSA) | 14 |  |  |

|   | 2.3          | Real-Time Embedded Systems                    | 15 |  |  |

|   |              | 2.3.1 Embedded Systems                        | 15 |  |  |

|   |              | 2.3.2 Real-Time Systems                       | 16 |  |  |

|   | 2.4          | System Model and Architecture                 | 16 |  |  |

|   | 2.5          | Metrics                                       | 18 |  |  |

| 3 | Rese         | earch Description                             | 21 |  |  |

|   | 3.1          | Scientific Contributions                      | 21 |  |  |

|   | 3.2          | Summary of Included Papers                    | 24 |  |  |

|   | 3.3          | Research Process and Methodology              | 28 |  |  |

| 4 | Rela         | ated Work                                     | 31 |  |  |

| 5 | Conclusions  |                                               |    |  |  |

|   | 5.1          | Summary and Conclusions                       | 35 |  |  |

|   | 5.2          | Future Work                                   | 36 |  |  |

#### Bibliography

38

## **II Included Papers**

| 6 | Paper A: Intelligent Data Processing using In-Orbit Advanced Al-<br>gorithms on Heterogeneous System Architecture |                                                                                                                       |          |  |  |  |

|---|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

|   | 6.1                                                                                                               | Introduction                                                                                                          | 47       |  |  |  |

|   |                                                                                                                   | 6.1.1 Contributions                                                                                                   | 48       |  |  |  |

|   |                                                                                                                   | 6.1.2 Organization                                                                                                    | 48       |  |  |  |

|   | 6.2                                                                                                               | Related Work                                                                                                          | 48       |  |  |  |

|   | 6.3                                                                                                               | Background                                                                                                            | 50       |  |  |  |

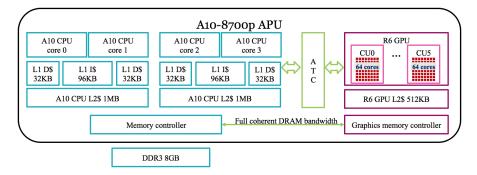

|   | 0.5                                                                                                               | 6.3.1 AMD A-Series A10-8700P APU                                                                                      | 50       |  |  |  |

|   |                                                                                                                   | 6.3.2 GIMME3 and GIMME4                                                                                               | 51       |  |  |  |

|   |                                                                                                                   | 6.3.3 Heterogeneous System Architecture                                                                               | 52       |  |  |  |

|   | 6.4                                                                                                               | Experiment Setup                                                                                                      | 52<br>54 |  |  |  |

|   | 0.4                                                                                                               | · ·                                                                                                                   | 54<br>55 |  |  |  |

|   |                                                                                                                   |                                                                                                                       | 55       |  |  |  |

|   |                                                                                                                   | 6.4.2 Configuration of Test Scenarios                                                                                 |          |  |  |  |

|   |                                                                                                                   | 6.4.3 Test Data                                                                                                       | 56       |  |  |  |

|   | ~ <b>-</b>                                                                                                        | 6.4.4 Evaluation Environment                                                                                          | 56       |  |  |  |

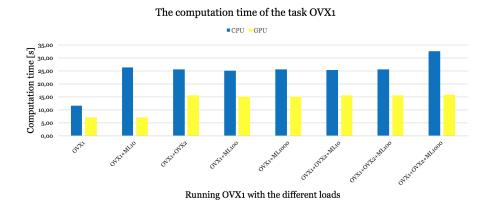

|   | 6.5                                                                                                               | Experiment Results                                                                                                    | 57       |  |  |  |

|   | 6.6                                                                                                               | Conclusion / Future Work                                                                                              | 59       |  |  |  |

|   | 6.7                                                                                                               | Test Data                                                                                                             | 59       |  |  |  |

|   |                                                                                                                   | 6.7.1 Source of the Test Data                                                                                         | 59       |  |  |  |

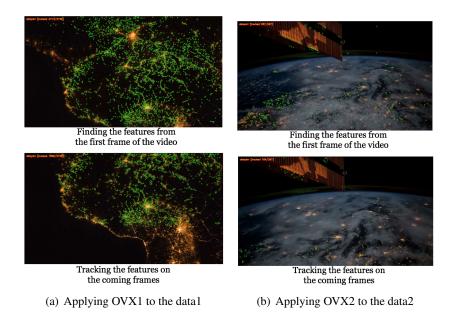

|   |                                                                                                                   | 6.7.2 Tracking Results                                                                                                | 60       |  |  |  |

|   | 6.8                                                                                                               | Pseudo Code for the Measurements of the Computation Time .                                                            | 61       |  |  |  |

|   | Bibl                                                                                                              | iography                                                                                                              | 62       |  |  |  |

| 7 | sum                                                                                                               | er B: A Trade-Off between Computing Power and Energy Con-<br>ption of On-Board Data Processing in GPU Accelerated In- | ~=       |  |  |  |

|   |                                                                                                                   | it Space Systems                                                                                                      | 65       |  |  |  |

|   | 7.1                                                                                                               | Introduction                                                                                                          | 67       |  |  |  |

|   |                                                                                                                   | 7.1.1 Contributions                                                                                                   | 68       |  |  |  |

|   |                                                                                                                   | 7.1.2 Organization                                                                                                    | 68       |  |  |  |

|   | 7.2                                                                                                               | Related work                                                                                                          | 69       |  |  |  |

|   | 7.3                                                                                                               | Background                                                                                                            | 70       |  |  |  |

|   |                                                                                                                   | 7.3.1 Real-time system                                                                                                | 70       |  |  |  |

|   |                                                                                                                   | 7.3.2 Heterogeneous computing                                                                                         | 71       |  |  |  |

|   |                                                                                                                   | 7.3.3 Advanced applications in satellite                                                                              | 72       |  |  |  |

|   | 7.4                                                                                                               | System Model                                                                                                          | 74       |  |  |  |

|   | 7.5                                                                                                               | Experimental design                                                                                                   | 75       |  |  |  |

|   |                                                                                                                   | 7.5.1 Algorithms                                                                                                      | 76       |  |  |  |

|   |                                                                                                                   | 7.5.2 Testbeds                                                                                                        | 77       |  |  |  |

|   |                                                                                                  | 7.5.3    | Experimental observations                          | 77              |  |  |  |  |

|---|--------------------------------------------------------------------------------------------------|----------|----------------------------------------------------|-----------------|--|--|--|--|

|   |                                                                                                  | 7.5.4    | Evaluation and Results                             | 80              |  |  |  |  |

|   | 7.6                                                                                              | Conclu   | usion                                              | 85              |  |  |  |  |

|   | Bibl                                                                                             | iography | y                                                  | 87              |  |  |  |  |

| 0 | <b>D</b>                                                                                         |          | obline De l'africa Televisió II dans como CDU hara | J               |  |  |  |  |

| 8 | Paper C: Enabling Radiation Tolerant Heterogeneous GPU-based<br>Onboard Data Processing in Space |          |                                                    |                 |  |  |  |  |

|   | 8.1                                                                                              |          |                                                    | <b>93</b><br>95 |  |  |  |  |

|   | 8.2                                                                                              |          | d work                                             | 96              |  |  |  |  |

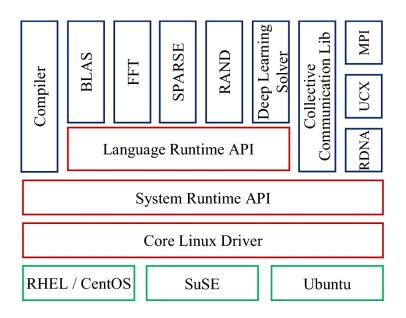

|   | 0.2                                                                                              | 8.2.1    | Heterogeneous computing architecture overview      | 97              |  |  |  |  |

|   |                                                                                                  | 8.2.2    | High performance computing tools in space          | 99              |  |  |  |  |

|   | 8.3                                                                                              |          | ng interface for modularity and form factor        | 101             |  |  |  |  |

|   | 8.4                                                                                              |          | -event effect mitigation middleware (SMM)          | 102             |  |  |  |  |

|   | 8.5                                                                                              | •        | n scenarios and application                        | 102             |  |  |  |  |

|   | 0.0                                                                                              | 8.5.1    | Applications                                       |                 |  |  |  |  |

|   | 8.6                                                                                              |          | are overview                                       | 108             |  |  |  |  |

|   | 8.7                                                                                              |          | gent data processing performance evaluation        | 109             |  |  |  |  |

|   | 017                                                                                              | 8.7.1    | Evaluation environment                             |                 |  |  |  |  |

|   |                                                                                                  | 8.7.2    | Experimental design                                | 110             |  |  |  |  |

|   |                                                                                                  | 8.7.3    | Results                                            |                 |  |  |  |  |

|   | 8.8                                                                                              | Conclu   | isions                                             |                 |  |  |  |  |

|   | Bibl                                                                                             |          | y                                                  |                 |  |  |  |  |

|   |                                                                                                  |          |                                                    |                 |  |  |  |  |

| 9 | Paper D: Simulation and Analysis of In-Orbit Applications under                                  |          |                                                    |                 |  |  |  |  |

|   |                                                                                                  |          | Effects on COTS Platforms                          | 121             |  |  |  |  |

|   | 9.1                                                                                              |          | uction                                             |                 |  |  |  |  |

|   |                                                                                                  | 9.1.1    | A. Contributions                                   | 123             |  |  |  |  |

|   | ~ <b>~</b>                                                                                       | 9.1.2    | B. Organization                                    |                 |  |  |  |  |

|   | 9.2                                                                                              |          | System architecture                                | 124             |  |  |  |  |

|   |                                                                                                  | 9.2.1    | A. System Model                                    |                 |  |  |  |  |

|   |                                                                                                  | 9.2.2    | B. Task Model                                      |                 |  |  |  |  |

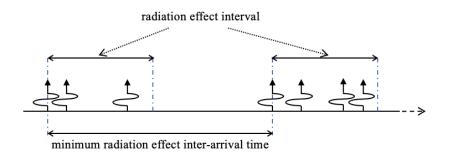

|   | ~ <b>~</b>                                                                                       | 9.2.3    | C. Radiation Effect Model                          |                 |  |  |  |  |

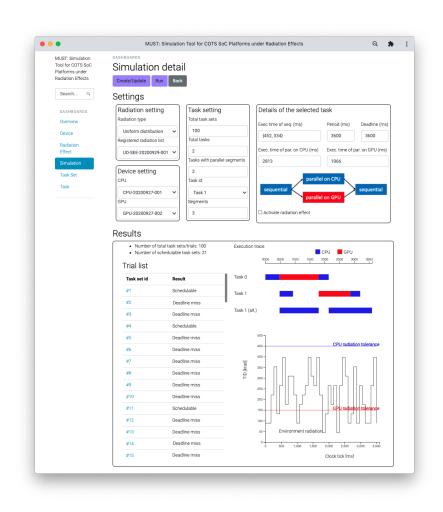

|   | 9.3                                                                                              |          | : Design and implementation                        |                 |  |  |  |  |

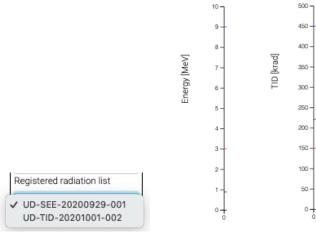

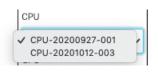

|   |                                                                                                  | 9.3.1    | A. Input & Output                                  | 129             |  |  |  |  |

|   |                                                                                                  | 9.3.2    | B. Design                                          | 132             |  |  |  |  |

|   |                                                                                                  | 9.3.3    | C. Simulation Mechanism                            | 132             |  |  |  |  |

|   | 0.4                                                                                              | 9.3.4    | D. Implementation                                  | 133             |  |  |  |  |

|   | 9.4                                                                                              |          | : Use case                                         | 134             |  |  |  |  |

|   |                                                                                                  | 9.4.1    | A. Use Case Description                            | 134             |  |  |  |  |

|   |                                                                                                  | 9.4.2    | B. Evaluation and Discussion                       | 134             |  |  |  |  |

|    | 9.5         | Related work and tools                                                                                      | 136        |

|----|-------------|-------------------------------------------------------------------------------------------------------------|------------|

|    | 9.6         | Conclusions                                                                                                 | 137        |

|    | Bibli       | ography                                                                                                     | 139        |

| 10 | Pape        | er E: Static Allocation of Parallel Tasks to Improve Schedula                                               | -          |

|    | bility      | y in CPU-GPU Heterogeneous Real-Time System                                                                 | 141        |

|    | 10.1        | Introduction                                                                                                | 143        |

|    |             | 10.1.1 Contributions                                                                                        | 144        |

|    |             | 10.1.2 Organization                                                                                         | 144        |

|    | 10.2        | Motivation                                                                                                  | 145        |

|    |             | System and task model                                                                                       | 146        |

|    |             | 10.3.1 System model                                                                                         | 146        |

|    |             | 10.3.2 Task Model                                                                                           | 147        |

|    | 10.4        | Heuristic Task Allocation Approaches                                                                        | 149        |

|    |             | 10.4.1 Non-Greedy Resource Allocation Heuristic Approach                                                    |            |

|    |             | (NHA)                                                                                                       | 149        |

|    |             | 10.4.2 Speedup Classifier based Heuristic Approach (SHA) .                                                  | 149        |

|    | 10 <b>-</b> | 10.4.3 Min-Min Approach (MMA)                                                                               | 150        |

|    | 10.5        | Synthetic Experiments                                                                                       | 151        |

|    |             | 10.5.1 Task set generation                                                                                  | 151        |

|    |             | 10.5.2 Comparative algorithms                                                                               | 152        |

|    |             | 10.5.3 Experiment setup                                                                                     | 152        |

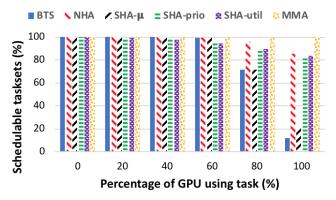

|    | 10.0        | 10.5.4 Result                                                                                               | 152        |

|    |             | Related work                                                                                                | 155        |

|    |             | Conclusions                                                                                                 | 156<br>157 |

|    | B1011       | ography                                                                                                     | 157        |

| 11 | -           | er F: Offloading Accelerator-intensive Workloads in CPU-GPU                                                 |            |

|    |             | rogeneous Processors                                                                                        | 161        |

|    |             | Introduction                                                                                                | 163        |

|    |             | Related Work                                                                                                |            |

|    |             | System Model                                                                                                |            |

|    |             | Proposed Workload Allocation Framework                                                                      | 168        |

|    | 11.5        | Offloading Techniques                                                                                       | 169        |

|    |             | 11.5.1 Baseline: Default Allocation Technique (DAT)                                                         | 170        |

|    |             | <ul><li>11.5.2 Naive Offloading Technique (NOT)</li></ul>                                                   | 170        |

|    |             |                                                                                                             | 171<br>171 |

|    |             | 11.5.4Speedup Classifier Based Technique (SCT)11.5.5Synchronized Servers Technique (SST)                    | 171        |

|    |             | 11.5.5       Synchronized Servers Technique (SST)         11.5.6       Efficient Offloading Technique (EOT) | 172<br>173 |

|    |             |                                                                                                             | 1/3        |

| 11.6 Experimental Evaluation                      | 174 |

|---------------------------------------------------|-----|

| 11.6.1 Task Set Generation and Experimental Setup | 174 |

| 11.6.2 Offloading Techniques                      | 175 |

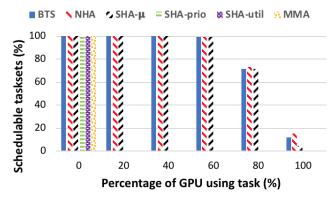

| 11.6.3 Evaluation Results                         | 175 |

| 11.7 Conclusion                                   | 180 |

| Bibliography                                      | 181 |

# Part I Thesis

# Chapter 1 Introduction

In the last two decades, the exploitation of small satellites and CubeSats<sup>1</sup> has rapidly increased for academic, commercial, and government intelligence applications [1, 2]. Space applications like for earth observation, deep space explorations, and communications, exploit on-board processing and reconstitute the role and use of small satellites from being a simple node of sensing data to a generator of big data and provider of efficient storage, and intelligent on-board decision making using the data, i.e., space computing. Numerous studies show that the intelligent on-board processing improves the use of the limited communication link bandwidth on small satellites [3, 4, 5], while it requires high-performance computing capability under the size, weight, and power (SWaP), radiation and real-time constraints.

As high-performance space computing technology is a key for the future of space missions, the interest in commercial-off-the shelf (COTS) heterogeneous platforms for space computing is growing vastly. Heterogeneous platforms employ different types of processing units on the same chip such as Central Processing Unit (CPU), Graphics Processing Unit (GPU), Field-Programmable Gate Array (FPGA), Digital Signal Processor (DSP), to mention a few. These platforms provide massive computation capabilities. However, these platforms make the systems more complex. For instance, the systems that utilize heterogeneous computing platforms are more prone to unpredictable timing behaviours compared to the systems that use single-core computing platforms [6]. The work presented in this thesis tackles the challenges to make efficient use of the different compute resources considering various bottlenecks and difficulties in heterogeneous computing platforms.

Furthermore, COTS platforms are usually wobbly against radiation effects

<sup>&</sup>lt;sup>1</sup>https://www.nasa.gov/content/what-are-smallsats-and-cubesats

without handling any radiation hardening. Besides, understanding of how COTS platforms react under radiation effects is less studied on the level of software and applications. Therefore, this thesis deals with synthetic simulations of radiation effects in order to assess timing predictability of real-time systems using COTS heterogeneous platforms.

As discussed earlier, heterogeneous platforms include multiple processing units and each of them can consist of multiple cores. Thus, this thesis provides a technique to support balanced use of heterogeneous processing units, while improving timing predictability of these platforms. Furthermore, we focused on an investigation of the trade-off between computing performance and power consumption while supporting schedulability of task sets. This investigation shows that our proposed techniques fit well with the embedded systems that are constrained by real-time and energy constraints.

#### **1.1** Thesis Goal and Research Challenges

The overall goal of the work in this thesis is

"to improve the timing predictability of real-time applications on heterogeneous computing platforms under harsh environments for on-board data processing (e.g., space computing) without degrading their computing performance and energy efficiency."

To achieve the goal, we target three core research challenges as follows:

**Research Challenge 1:** To identify the key factors that affect timing predictability and power consumption in real-time applications on heterogeneous CPU-GPU platforms without degrading their computing performance.

**Research Challenge 2:** To improve schedulability of real-time applications running on heterogeneous computing platforms by manipulating the identified factors.

**Research Challenge 3:** To provide techniques and tools to schedule, analyze and simulate real-time applications running on heterogeneous computing platforms, in particular, under harsh environments.

#### **1.2** Outline of the Thesis

The thesis is based on a collection of six peer-reviewed publications. The thesis consists of two parts:

**Part I** includes the first five chapters. In Chapter 1, an introduction to the thesis has been provided. The thesis goal and research challenges are introduced in this chapter. Chapter 2 presents the preliminary concepts that are considered throughout the thesis. In Chapter 3, we discuss the contributions and research methodology in the thesis. We present the related work in Chapter 4, and the conclusion and the future work are presented in Chapter 5.

**Part II** provides the collection of six peer-reviewed publications considered as the scientific contributions of the thesis. This part constitutes Chapters 6-11.

## Chapter 2

## Background

This chapter provides the required background information following the motivation of the thesis that starts with space computing, and continues with necessary hardware/software solution (heterogeneous computing) with required real-time constraint.

### 2.1 Space Computing

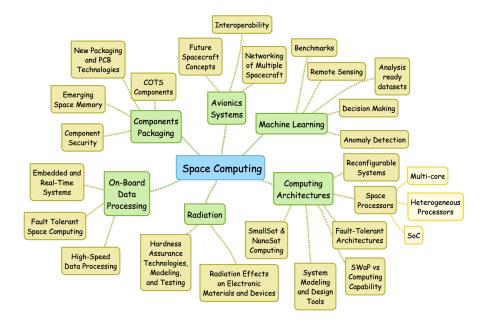

Space computing started to gain considerable attention of the research computing with the advent of the IEEE Space Computing Conference (SCC)<sup>1</sup> since 2006. Previously, this event was know as Fault Tolerant Space Computing conference/workshop. As space computing performs under harsh environments with radiation, it is closely related to the research introduced in IEEE Nuclear & Space Radiation Effects Conference (NSREC)<sup>2</sup>. Based on active topics covered by the SCC and NSREC conferences, we illustrate space computing in Figure 2.1. Among these topics, this thesis concerns more about COTS components, on-board data processing, radiation, heterogeneous space processors using machine learning benchmarks for intelligent decision making. In this section, we provide more information about on-board data processing and radiation.

#### 2.1.1 On-Board Data Processing

Space is a perfect example for considering real-time system applications as many on-board functions in spacecraft and satellites are constrained by soft

<sup>&</sup>lt;sup>1</sup>https://spacecomputing.ecs.baylor.edu/

<sup>&</sup>lt;sup>2</sup>http://www.nsrec.com/

Figure 2.1: Space computing

and hard real-time requirements (see Section 2.3.2 for more details about soft and hard real-time systems). Any failure such as losing control of a system or unable to transfer data may end up in a catastrophic result as it is not possible to fix the devices in orbit or deep space. In order to reduce delays and have more predictable activities, the role of on-board data processing becomes significant. However, due to SWaP (size, weight and power) constraints along with radiation hardiness problem in space, the development of space systems usually encounter limitations which are not always experienced on the earth. The design and development of the on-board computer need to overcome these limitations.

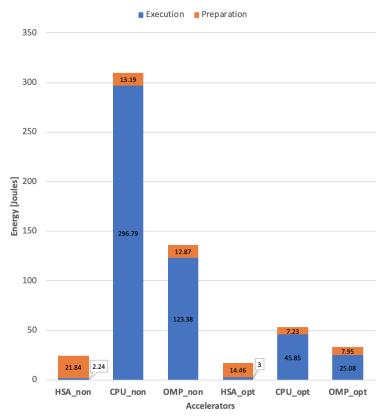

As a heterogeneous architecture, the combination of CPU + FPGA and/or CPU + DSP is broadly employed for on-board computers in space [7]. However, these combinations could not support massive amount of computations required by the intelligent on-board data processing systems. These heterogeneous architecture combinations complemented by GPUs can overcome the above mentioned limitation by running multiple parallel executions and faster memory accesses. Thus, heterogeneous architectures that include CPU, GPU and FPGA can offer an efficient computation solution for on-board data processing systems. In such an architecture, an FPGA can be used for receiving sensors' data with shorter delays, a CPU can act as a controller between the FPGA and GPU, and the GPU can process heavy computations.

#### 2.1.2 Radiation Effects

Radiation effects increase the complexity of space systems. As radiation effects are cumulative on the one hand, although the dose of space radiation is mostly low, its risk increases by the total time traveled in space [8, 9]. This characteristic is described by total dose of radiation, i.e., total ionizing dose (TID). Developing shielding materials or radiation-hardened products in order to mitigate radiation effects in orbit components could worsen the other limitations such as size, weight, and power, cost, and development time. On the other hand, particles with high energy such as electrons cause electrostatic discharge, single-event effects (SEEs). Thus, radiation effects can hinder the usage of commercial off-the-shelf (COTS) technologies that have been successful in the systems used the earth, such as COTS system on chip (SoC), including the use of integrated graphics processing units (GPUs), which improve the quality of onboard data processing [10]. We introduce safety allowable range of both particle energy and TID as radiation tolerance in this thesis and consider that an idea of radiation tolerance improves space computing.

### 2.2 Heterogeneous Computing

The role of heterogeneous computing has been growing dramatically in industrial applications [11]. Employing multiple types of processing units makes the embedded systems robust. Freund and Conwell define heterogeneous computing as follows:

**Definition 2.1:** "Heterogeneous computing is the well-orchestrated and coordinated effective use of a suite of diverse high-performance machines (including parallel machines) to provide super speed processing for computationally demanding tasks with diverse computing needs." *R. F. Freund and D. S. Conwell* [12]

We re-define the above definition using a new term "heterogeneous processor" instead of machines and consider it in this thesis. "Heterogeneous computing is the well-orchestrated and coordinated effective use of a suite of on- and/or off-chip heterogeneous processing units to provide high-performance processing for computationally demanding tasks with diverse computing needs." With this definition, the focus of computation shifts from a machine to a processing unit (PU), and the location of them distinguished by either on- or off-chip. In case of off-chip, processing units communicate with each other via diverse types of interconnection and network, while processing units employed in the same die for on-chip. The thesis mostly touches on-chip heterogeneous processing units as heterogeneous processing units.

Heterogeneous processing units can employ the same type of naming with different instruction set architecture and/or even different clock speed (e.g., ARM Cortex CPU + Nvidia Denver CPU), while commonly considered to employ the combinations of different types of naming processors such as CPU + GPU, CPU + FPGA and etc. In order to study heterogeneous computing, not only processor types, but also heterogeneous architectures, memory management and interconnection are crucial.

#### 2.2.1 Heterogeneous Architectures

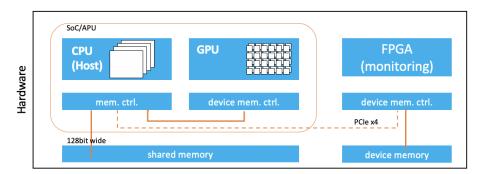

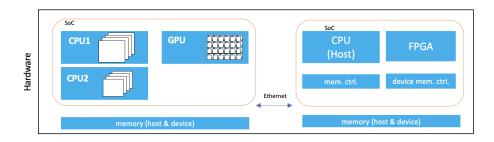

As defined in Section 2.2, heterogeneous computing appears with different architectures, as described heterogeneous architectures. Figures 2.2, 2.3, 2.4, and 2.5 illustrate the well-known heterogeneous architectures as some of them appear in satellites and autonomous vehicles.

Figure 2.2: GIMME3 and GIMME4 platforms by Unibap AB and Mälardalen University based on AMD APU (CPU and integrated GPU).

The heterogeneous architecture described in Figure 2.2 consists of three different processing units, CPU, GPU, and FPGA. CPU and GPU are in a system on a chip (SoC) and connect to shared memory. The purpose of external processing unit, FPGA, is to monitor the health of SoC. FPGA interconnects with CPU via PCIexpress and has its own memory. The SoC illustrated in Figure 2.2 is called Accelerated Processing Units (APU), that is commonly known as integrated GPU. In this platform, APU considers a computer architecture specialized for heterogeneous computing, i.e., Heterogeneous System Architecture (HSA).

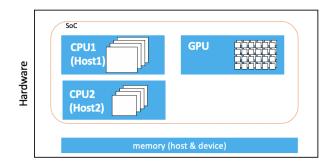

Figure 2.3: Jetson TX platform employs ARM big.LITTLE CPUs (ARM Cortex CPUs and Nvidia Denver CPUs) with Nvidia GPU.

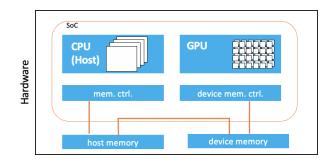

Figure 2.4: GPU4S by Barcelona Supercomputing Center based on Jetson Xavier platform (ARM CPU and Nvidia GPU).

Both heterogeneous architectures illustrated in Figures 2.3 and 2.4 contain only SoCs. Figure 2.4 describes that homogeneous CPU cores and GPU are employed in the same SoC and connect to independent memories. On the other hand, the SoC illustrated in Figure 2.3 consists of heterogeneous CPU cores and GPU. In other words, two CPUs from different vendors and different frequencies are employed in the SoC. This architecture is known as the big.LITTLE CPUs architecture. In order to improve heterogeneous computing, the Big.LITTLE CPUs can be used with clustered switching, in-kernel switching, and heterogeneous multi-processing task migration and scheduling mechanisms [13].

The heterogeneous architecture illustrated in Figure 2.5 consists of two SoCs, which are connected through Ethernet. One of them includes two CPUs with different computing capacities and GPU. Another SoC comprises CPU and FPGA.

Figure 2.5: On-board platform for the University of Georgia's satellite (Jetson TX2i + Smart Fusion).

#### 2.2.2 Memory Model & Interconnection

#### **Memory Model**

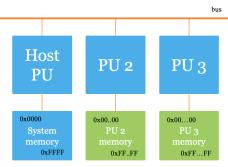

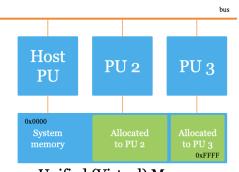

In Figures 2.6, 2.7, and 2.8, most common memory models for heterogeneous architectures are described. In these models, we do not focus on the interconnection between PUs and between PUs and memories, while the relation between memories of different PUs are crucial. As illustrated in Figure 2.6, each PU has own allocated memory and independent memory address, i.e., it is called Multi Memory Model (MMM). In this case, data should be transferred between different memories and addresses should be handled as well. Heterogeneous architectures with external PUs tend to have this memory model such as the platform depicted in Figure 2.5. In unified (virtual) memory model (UVM) as illustrated in Figure 2.7, PUs connect to a physical memory. However, each PU should be connected to allocated area only. This means, data should still be transferred/copied between memory areas when different PUs need to access the same data. UVM uses a memory address system for all the PUs and data will be copied in the same physical memory. Hence, data transfer time is less compared to UVM.

As depicted in Figure 2.8, Unified Shared Memory (USM) allows to access to the same data from different PUs. This eliminates unnecessary data transfer and copy. However, it requires advanced interconnection techniques.

#### Interconnection

Interconnection is the main key to the challenges of heterogeneous memory management, although both software and hardware solutions are required. There exist the following four specifications focused on the interconnection

Multi Memory Model

Figure 2.6: Multi Memory Model.

Unified (Virtual) Memory

Figure 2.7: Unified (Virtual) Memory.

and buses.  $CCIX^3$  (Cache Coherent Interconnect for Accelerators), Open-CAPI<sup>4</sup> (Open Coherent Accelerator Processor Interface), Gen-Z<sup>5</sup> and CXL<sup>6</sup> (Computer Express Link). Only CXL is proposed by an Intel-driving consortium, and both AMD and ARM are announced to join this consortium. In this sense, CXL has a vast potential that could be upgraded to the industry de-facto standard for the interconnection between host and devices.

<sup>3</sup> CCIX https://www.ccixconsortium.com/

<sup>&</sup>lt;sup>4</sup>OpenCAPI https://opencapi.org/

<sup>&</sup>lt;sup>5</sup>Gen-Z https://genzconsortium.org/

<sup>&</sup>lt;sup>6</sup>CXL https://www.computeexpresslink.org/

Figure 2.8: Unified Shared Memory.

#### 2.2.3 Heterogeneous System Architecture (HSA)

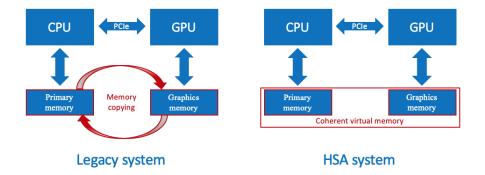

Different types of specifications and designs of the processing units bring complexities for the development process from cost and timing perspective. To tackle these problems, HSA Foundation [14] has been established by multiple leading hardware vendors to develop the Heterogeneous System Architecture (HSA) specification for reducing the complexity of heterogeneous computations and providing the developer-friendly environments. The main properties of HSA are described with memory handling, software stack, and interconnection.

Figure 2.9: Memory structure between a non-HSA system and an HSA system.

**Memory handling:** The HSA aims to ease the development process on the heterogeneous platform by providing a development environment to the programmers that is similar to the environment for traditional systems, i.e., homogeneous systems. The HSA provides unified coherent memory for host and devices that saves time for transferring data between different physical memories, i.e., there is no memory copy between different physical memories, e.g., primary and graphics memories (see Figure 2.9).

**Software stack:** As a part of the HSA, AMD introduces an initiative GPUOpen, an open source software stack, including, but not limited to, kernel level driver, runtime environment, profiling tools, computer vision and machine learning libraries such as ROCm<sup>7</sup>, CodeXL<sup>8</sup>, AMD OpenVX<sup>9</sup>, MIOpen<sup>10</sup> as well as Tensorflow<sup>11</sup> on AMD GPUs. From TensorFlow 2.0, AMD has fully upstreamed their support.

**Interconnection:** While HSA covers interconnection between different devices, it needs to be collaborated with the interconnection specifications. As CXL is an open standard interconnection and only accepted by all the main vendors such as Intel, AMD, and ARM, the relation between HSA and CXL is crucial and it could co-exist as follows. While HSA is located at a high level, which is close to the developers for reducing the complexity of the development of heterogeneous systems, CXL is directly focused on hardware devices, which is at a low level. This indicates the possibility of the co-existence of HSA and CXL.

### 2.3 Real-Time Embedded Systems

#### 2.3.1 Embedded Systems

Embedded systems are found in almost all electronic products covering diverse domains such as consumer products, business, military, aerospace and so on. As they are embedded, embedded systems are mostly remain hidden from the end users. A definition of an embedded system is described as follows:

**Definition 2.2:** "An embedded system is a combination of computer hardware and software – and perhaps additional parts, either mechanical or electronic – designed to perform a dedicated function." M. Barr and A. Massa [15]

<sup>&</sup>lt;sup>7</sup>ROCm https://github.com/RadeonOpenCompute/ROCm

<sup>&</sup>lt;sup>8</sup>CodeXL https://gpuopen.com/compute-product/codexl/

<sup>&</sup>lt;sup>9</sup>OpenVX https://gpuopen.com/compute-product/amd-openvx/

<sup>&</sup>lt;sup>10</sup>MIOpen https://gpuopen.com/compute-product/miopen/

<sup>&</sup>lt;sup>11</sup>Tensorflow https://rocm.github.io/tensorflow.html

#### 2.3.2 Real-Time Systems

A real-time system is a system that reacts to external events in a timely manner. This means that not only the accuracy of the result, but also the timeliness is a crucial factor for the accuracy of the system. Hence, a real-time embedded system is an embedded system, which reacts to its environment in a timely manner.

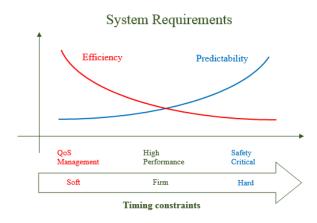

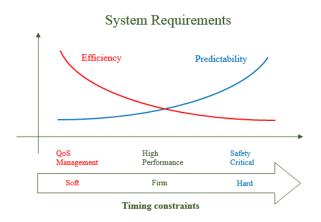

Figure 2.10: A real-time system requirements.<sup>12</sup>

As illustrated in Figure 2.10, real-time systems can be divided into a hard, firm and soft [16] real-time system from perspective of the timing constraints. The hard real-time system must pass all specified timing constraints. If the system misses a constraint (e.g., a deadline) once, it results in failure leading to a fatality and/or big financial or environmental damage. Therefore, many hard real-time systems are considered to be safety critical. In a soft real-time system, one or more deadline misses may be tolerated at the cost of lower quality of service. A firm real-time system is between hard and soft real-time systems.

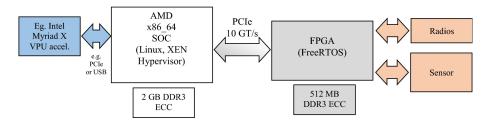

### 2.4 System Model and Architecture

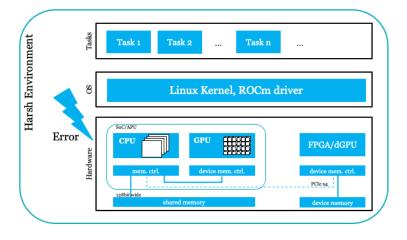

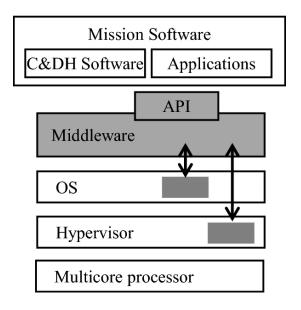

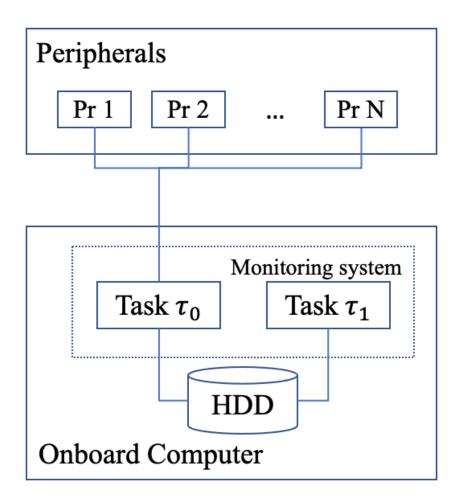

We consider a system, which consists of applications comprising of a task set (i.e., a set of applications, software stack), an operating system (kernel including drivers), and a hardware platform as illustrated in Figure 2.11. In

<sup>&</sup>lt;sup>12</sup>http://www.artist-embedded.org/docs/Events/2008/RT-Kernels/SLIDES/s1-Intro.pdf

addition, in the system architecture, we consider an error to hardware platform, which appears as an interference task to the task set. In this thesis, an error is a radiation effect that is generated from the surrounding harsh environment and interferes with the hardware platform including its devices such as processing units, memory and so on.

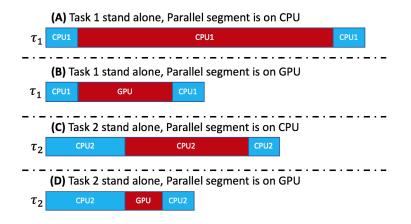

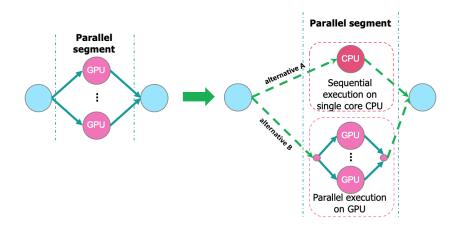

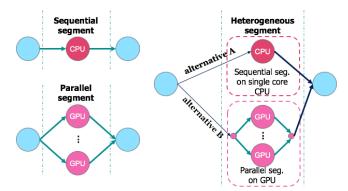

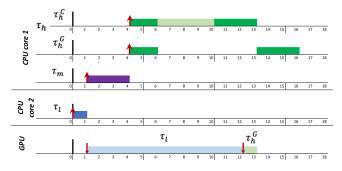

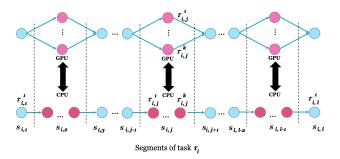

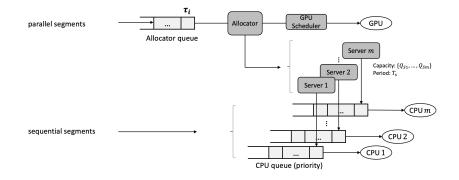

Figure 2.11: System Architecture.

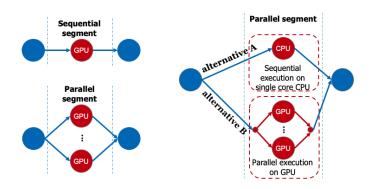

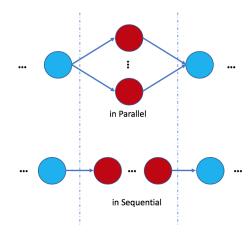

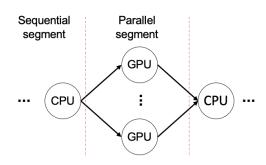

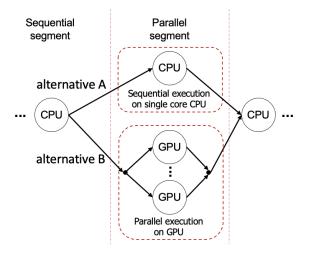

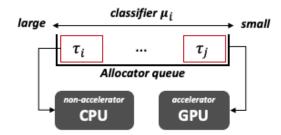

A task in the task set consists of parallel and sequential segments and is represented by the fork/join task model [17]. We assume that sequential segments should be executed only on CPU while parallel segments can be executed in parallel on GPU or on CPU sequentially. Moreover, in this thesis, we consider an extension of the fork-join task model by adopting the notion of heterogeneous segments. A heterogeneous segment can either be mapped to a GPU for parallel execution (alternative B) or to a CPU for sequential execution of the same code segment (alternative A), see Figure 2.12.

The thesis considers that the hardware platform employs a heterogeneous architecture, which may include three types of processing units; host device as CPU, integrated accelerators such as integrated GPU (iGPU), and discrete accelerators such as discrete GPU (dGPU) and/or FPGA (see Figure 2.11). We assume that the hardware platform is HSA-compliant. In some cases, to narrow the setting, at least processing units in system-on-chip (SoC) side should be compliant with the HSA. From the power utilization perspective, on one hand, host device and integrated accelerators share the same power controller, i.e., both turn on and off at the same. On the other hand, discrete accelerators have a dedicated power controller for each, which means that the combinations, "Host-and-Integrated-Accelerators" and "Host-and-Discrete-Accelerators", have

Figure 2.12: Sequential, parallel and alternative executions of parallel segments of tasks.

different amount of power consumption. Furthermore, from the memory structure perspective, "Host-and-Integrated-Accelerators" connects to the shared memory while "Host-and-Discrete-Accelerators" accesses to the virtual shared memory.

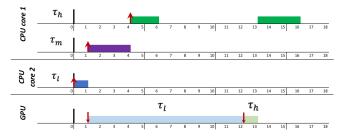

In this thesis, the following three reference platforms are considered: CPU + iGPU, CPU + iGPU + FPGA, and CPU + dGPU. Although it is available to use FPGA, our focus on the thesis is only CPU and GPU. CPU scheduling is realized by a partitioned fixed-priority scheduler and we further assume that the execution on CPUs is preemptable. In contrast, the execution on GPU is not preemptable. GPU allows to execute tasks with non-preemptive fixed priority scheduling.

### 2.5 Metrics

In this thesis, the following metrics are considered in the investigation and experimental evaluation of heterogeneous computing architectures: computing performance, energy efficiency, timing predictability, and radiation tolerance. Use of these metrics in different research methods is explained in Section 3.3.

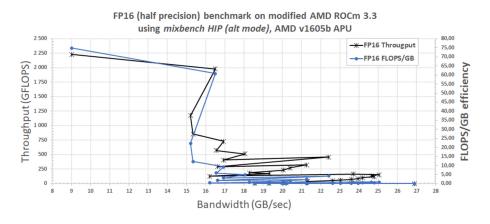

**Computing performance** describes how fast tasks are calculated on the given processing units. Hence, this metric presents computing potential of platforms/processing units. A unit of time, second (s), is used for this metric and less computation time shows faster computing performance. There are other ways to express this metric such as FLOPS (floating-point operations per second). In the contributed papers, these expressions are used to give information about the reference platforms at a glance.

Energy efficiency introduces how less power is consumed by the given

processing units to compute tasks. A unit of energy, joule (J), is chosen to describe this metric. A smaller value of power consumption corresponds to more energy efficiency. Energy efficiency is a metric to consider power consumption on the systems/platforms.

**Timing predictability** presents how systems fulfill the given timing constraints. We consider a system is predictable if all tasks in this system meet their timing requirements [18]. Timing predictability of a system is related to proving, demonstrating or verifying the fulfillment of the timing requirements (e.g., deadline miss) that are specified on the system [19]. In order to consider the timing requirements of tasks in task sets, we conduct schedulability analysis of task sets.

**Radiation effect and tolerance** express how much high energy particles are present in the environment and what is tolerance of the given components in the systems against the radiation effects. A unit of both radiation effect and tolerance can be either [eV] or [rad] in the cases based on particle energy or total ionizing dose, respectively.

### Chapter 3

# **Research Description**

### 3.1 Scientific Contributions

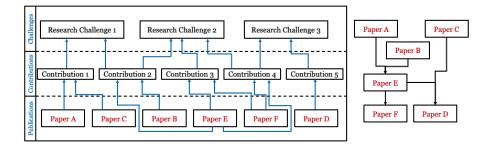

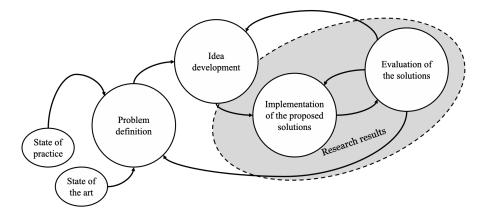

To achieve the thesis goal, the thesis provides five scientific contributions (SCs), which address the research challenges presented in Section 1.1. These contributions are encapsulated in six peer-reviewed research publications (Papers A-F). Mapping of the research challenges, contributions and publications is shown in Figure 3.1.

**Scientific Contribution 1:** Investigation of the fundamental characteristics of different types of heterogeneous architectures focusing on computation-time and power-consumption efficiency.

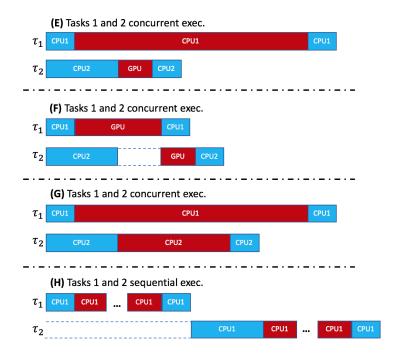

Motivation and summary of the contribution: This contribution helps to understand the current characteristics of heterogeneous platforms. By using the computing performance and energy efficiency metrics, we characterize various computing units in heterogeneous computing platforms. According to our prior knowledge, some tasks are suitable for parallel computing while some tasks are executable only in a sequential manner. Computer vision and machine learning applications are representations of parallelizable applications, and we consider these type of applications in Papers A and C. Our investigations aim to understand what kind of applications (i.e., under what kind of conditions, applications) are suitable to run on GPU compared to CPU or vice versa. As a result, we experienced that the execution of parallel applications on GPU boosts up to 238 times computing performance and consumes 13.5 times less energy, compared to CPU. Although applications that include the smaller numbers of parallel executions are suitable to run on CPU from the computing performance aspect, all parallel applications consumed less energy on GPU compared to CPU in our reference platforms. This contribution addresses Research Challenge 1.

**Scientific Contribution 2:** Proposing and evaluating a task model and allocation algorithms based on the model for real-time applications that run on CPU-GPU heterogeneous computing platforms.

**Motivation and summary of the contribution:** Based on the results acquired by addressing SC 1 and literature review, we extract and propose a novel task model for applications that run on heterogeneous processors, which allows alternative executions of parallel segments of tasks on heterogeneous processing units. By allowing alternative executions, parallel segments can be allocated to an appropriate processing unit with higher computation performance and less power consumption. Alternative executions of parallel segments are investigated in Papers B and E. While Paper B presents the idea of alternative executions of parallel segments of tasks, Paper E considers effects of the alternative executions on the timing behaviours of the applications. As an achievement, the appropriate use of heterogeneous processing units for parallel segments can decrease the total energy consumption of systems up to 64.3%. This contribution addresses Research Challenges 1 and 2.

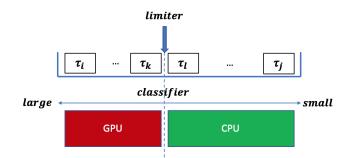

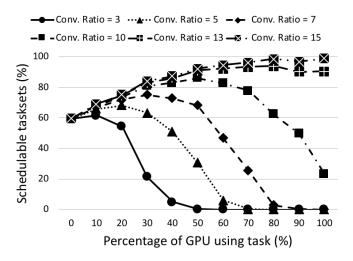

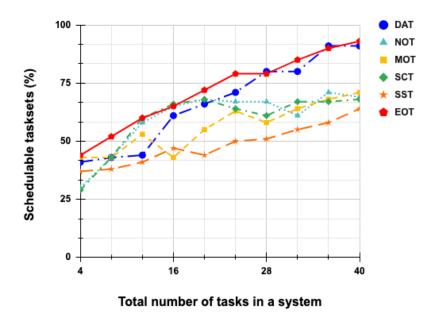

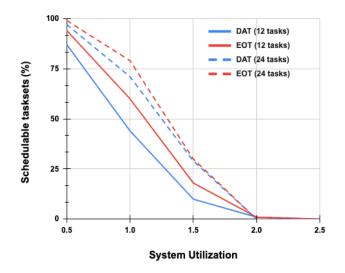

**Scientific Contribution 3:** Proposing and evaluating a new technique that utilizes the task model to improve schedulability of real-time applications running on COTS heterogeneous computing platforms.

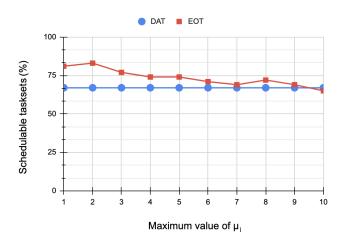

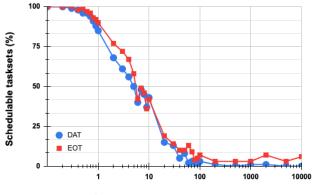

**Motivation and summary of the contribution:** Based on the achievements of SC 2 and a literature review, we propose solutions which aim at improving schedulability of the task sets on heterogeneous computing platforms. We integrate these solutions to the timing analysis proposed for CPU-GPU heterogeneous platforms. The solutions increase the number of schedulable task sets up to 90% compared to the existing solutions, while mitigating accelerator intensive loads. The contribution covers both static and dynamic scheduling of task sets. This contribution is discussed in Papers E and F in detail and addresses Research Challenge 2.

**Scientific Contribution 4:** Proposing a server-based scheduling technique that utilizes the proposed task model to improve the schedulability of real-time applications on CPU-GPU heterogeneous platforms.

**Motivation and summary of the contribution:** This contribution utilizes the task model and proposes a server-based scheduling technique for real-time systems that run on CPU-GPU heterogeneous computing platforms. Papers E and F cover this contribution. Paper E focuses on static allocation of tasks, and Paper F considers dynamic allocation of tasks. The evaluation results indicate

that one of the proposed techniques based on dynamic scheduling can schedule up to 16% more task sets compared to the traditional non-offloading technique. This contribution addresses Research Challenges 2 and 3.

**Scientific Contribution 5:** Developing a simulation framework and a tool considering the effects of different radiation tolerance of heterogeneous processing units on the schedulability of real-time applications under harsh environments.

**Motivation and summary of the contribution:** As radiation effects limits the usability of most of the state-of-the-art COTS technologies from use in space, this contribution presents a simulation framework and a tool to simulate real-time applications under harsh environments using heterogeneous processing units with different radiation tolerances. The simulation tool supports processing units with different characteristics of computing potential, radiation tolerance, as well as different type of processing units such as CPU and GPU. Artificial patterns of single-event effects can be introduced, for example, the patterns generated by using Poisson distribution, and other well-known mathematical distributions. In addition, the simulation tool employs the task model proposed in SC2 and helps to extend the study of heterogeneous processing units under the environments with radiation effects. This contribution is discussed in Paper D and addresses Research Challenge 3 together with SC 4.

As illustrated in Figure 3.1, Paper E proposes a solution based on Papers A and B. Papers A, B, and C focus on practical experiments on real physical platforms, while Papers E and F propose solutions for heterogeneous computing. Paper F is extended work to Paper E. Paper D is based on Papers E and C. It is about a simulation tool to support designers in choosing necessary heterogeneous processing units.

Figure 3.1: Mapping of the research challenges, contributions and publications

### **3.2 Summary of Included Papers**

**Paper A:** Intelligent Data Processing using In-Orbit Advanced Algorithms on Heterogeneous System Architecture

Nandinbaatar Tsog, Moris Behnam, Mikael Sjödin, Fredrik Bruhn. Published in the Proceedings of the 39th International IEEE Aerospace Conference, March 2018.

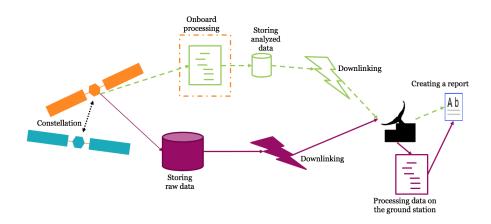

Abstract: In recent years, commercial exploitation of small satellites and CubeSats has rapidly increased. Time to market of processed customer data products is becoming an important differentiator between solution providers and satellite constellation operators. Timely and accurate data dissemination is the key to success in the commercial usage of small satellite constellations which is ultimately dependent on a high degree of autonomous fleet management and automated decision support. The traditional way for disseminating data is limited by on the communication capability of the satellite and the ground terminal availability. Even though cloud computing solutions on the ground offer high analytical performance, getting the data from the space infrastructure to the ground servers poses a bottleneck of data analysis and distribution. On the other hand, adopting advanced and intelligent algorithms onboard offers the ability of autonomy, tasking of operations, and fast customer generation of low latency conclusions, or even real-time communication with assets on the ground or other sensors in a multi-sensor configuration. In this paper, the advantages of intelligent onboard processing using advanced algorithms for Heterogeneous System Architecture (HSA) compliant onboard data processing systems are explored. The onboard data processing architecture is designed to handle a large amount of high-speed streaming data and provides hardware redundancy to be qualified for the space mission application domain. We conduct an experimental study to evaluate the performance analysis by using image recognition algorithms based on an open source intelligent machine library 'MIOpen' and an open standard 'OpenVX'. OpenVX is a cross-platform computer vision library.

**Paper B:** A Trade-Off between Computing Power and Energy Consumption of On-Board Data Processing in GPU Accelerated In-Orbit Space Systems Nandinbaatar Tsog, Saad Mubeen, Mikael Sjödin, Fredrik Bruhn. Published in the Transactions of JSASS, Aerospace Technology Japan, September 2021.

Abstract: On-board data processing is one of the prior on-orbit activities that

improves the performance capability of in-orbit space systems such as deepspace exploration, earth and atmospheric observation satellites, and CubeSat constellations. However, on-board data processing encounters higher energy consumption compared to traditional on-board space systems. This is because the traditional space systems employ simple processing units such as single-core microprocessors as the systems do not require heavy data processing. Moreover, solving the radiation hardness problem is crucial in space, and adopting a new processing unit is challenging.

In this paper, we consider a Graphics Processing Unit (GPU) accelerated in-orbit space system for on-board data processing. According to prior works, there exist radiation-tolerant GPU, and the computing capability of systems is improved by using heterogeneous computing method. We conduct experimental observations of energy consumption and computing potential using this heterogeneous computing method in our GPU accelerated in-orbit space systems. The results show that the proper use of GPU increases computing potential with 10-140 times and consumes between 8-130 times less energy. Furthermore, the entire task system consumes 10-65% of less energy compared to the traditional use of processing units.

## **Paper C:** Enabling Radiation Tolerant Heterogeneous GPU-based Onboard Data Processing in Space

Fredrik C. Bruhn, Nandinbaatar Tsog, Fabian Kunkel, Oskar Flordal, Ian Troxel. Published in the CEAS Space Journal, June 2020.

**Abstract:** The last decade has seen a dramatic increase in small satellite missions for commercial, public, and government intelligence applications. Given the rapid commercialization of constellation-driven services in Earth Observation, situational domain awareness, communications including machine-tomachine interface, exploration etc., small satellites represent an enabling technology for a large growth market generating truly Big Data. Examples of modern sensors that can generate very large amounts of data are optical sensing, hyperspectral, Synthetic Aperture Radar (SAR), and Infrared imaging. Traditional handling and downloading of Big Data from space requires a large onboard mass storage and high bandwidth downlink with a trend towards optical links. Many missions and applications can benefit significantly from onboard cloud computing similarly to Earth-based cloud services. Hence, enabling space systems to provide near real-time data and enable low latency distribution of critical and time sensitive information to users. In addition, the downlink capability can be more effectively utilized by applying more onboard processing to reduce the data and create high value information products. This paper discusses current implementations and roadmap for leveraging high performance computing tools and methods on small satellites with radiation tolerant hardware. This includes runtime analysis with benchmarks of convolutional neural networks and matrix multiplications using industry standard tools (e.g., TensorFlow and PlaidML). In addition, a 1/2 CubeSat volume unit (0.5U) (10×10×5 cm3) cloud computing solution, called SpaceCloud<sup>TM</sup> iX5100 based on AMD 28 nm APU technology is presented as an example of heterogeneous computer solution. An evaluation of the AMD 14 nm Ryzen APU is presented as a candidate for future advanced onboard processing for space vehicles.

**Paper D:** Simulation and Analysis of In-Orbit Applications under Radiation Effects on COTS Platforms

Nandinbaatar Tsog, Saad Mubeen, Moris Behnam, Mikael Sjödin, Fredrik Bruhn.

Published in the Proceedings of the 42nd International IEEE Aerospace Conference, March 2021.

Abstract: Radiation effects research is crucial as it defines risk to both human bodies and spacecraft. Employing radiation-hardened products is one way to mitigate radiation effects on in-orbit systems. However, radiation effects prohibit most of the state-of-the-art commercial off-the-shelf (COTS) technologies from use in space. Furthermore, radiation effects on software components are less studied compared to hardware components. In this work, we introduce a simulation tool that simulates and performs post-simulation analysis of the impact of radiation effects on schedulability of the software task sets that execute on COTS system-on-chip (SoC) platforms within in-orbit systems. In order to provide a meaningful verification environment, single-event effects (SEEs) are introduced as aleatory disturbances characterized by probability distribution of occurrence using their predefined models. The tool supports interoperability with several other tools as it uses the extensible markup language (XML) model files for input and output, i.e., for importing input task sets and radiation effects and exporting the simulation and analysis results. The proposed tool is extensively by running simulations using a use case of an in-orbit onboard monitoring system.

# **Paper E:** Static Allocation of Parallel Tasks to Improve Schedulability in GPU Accelerated Real-Time Systems

Nandinbaatar Tsog, Matthias Becker, Fredrik Bruhn, Moris Behnam, Mikael Sjödin.

Published in the Proceedings of the 45th Annual Conference of the IEEE Industrial Electronics Society (IECON), October 2019.

**Abstract:** Autonomous driving is one of the main challenges of modern cars. Computer visions and intelligent on-board decision making are crucial in autonomous driving and require heterogeneous processors with high computing capability under low power consumption constraints. The progress of parallel computing using heterogeneous processing units is further supported by software frameworks like OpenCL, OpenMP, CUDA, and C++AMP. These frameworks allow the allocation of parallel computation on different compute resources. This, however, creates a difficulty in allocating the right computation segments to the right processing units in such a way that the complete system meets all its timing requirements. In this paper, we consider pre-runtime static allocations of parallel tasks to perform their execution either sequentially on CPU or in parallel using a GPU. This allows for improving any unbalanced use of GPU accelerators in a heterogeneous environment. By performing several heuristic algorithms, we show that the overuse of accelerators results in a bottle-neck of the entire system execution. The experimental results show that our allocation schemes that target a balanced use of GPU improves the system schedulability up to 90%.

**Paper F:** Offloading Accelerator-intensive Workloads in CPU-GPU Heterogeneous Processors

Nandinbaatar Tsog, Saad Mubeen, Fredrik Bruhn, Moris Behnam, Mikael Sjödin.

Published in the Proceedings of the 26th International Conference on Emerging Technologies and Factory Automation (ETFA), September 2021.